Difference between revisions of "CSC270 Homework 2 2011"

(→Problem #1) |

|||

| (2 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

--[[User:Thiebaut|D. Thiebaut]] 15:40, 3 February 2011 (EST) | --[[User:Thiebaut|D. Thiebaut]] 15:40, 3 February 2011 (EST) | ||

---- | ---- | ||

| − | < | + | <br /> |

| − | < | + | <br /> |

| − | <br | + | <br /> |

| − | |||

| − | |||

<bluebox> | <bluebox> | ||

This assignment deals with minterms, Maxterms, Nands and Nors. You can work on this assignment in pairs. The due date is Friday 2/11 at midnight. | This assignment deals with minterms, Maxterms, Nands and Nors. You can work on this assignment in pairs. The due date is Friday 2/11 at midnight. | ||

</bluebox> | </bluebox> | ||

| + | <br /> | ||

| + | <br /> | ||

| + | __TOC__ | ||

| + | <br /> | ||

| + | <br /> | ||

=Problem #1= | =Problem #1= | ||

| Line 20: | Line 23: | ||

: Make sure you explain why this gate is, or is not, a universal gate. A simple yes or no answer will not get any credit! | : Make sure you explain why this gate is, or is not, a universal gate. A simple yes or no answer will not get any credit! | ||

| + | |||

| + | ;Question 2 | ||

| + | : Is the XOR gate (Y =a'.b + a.b' ) a universal gate? Why or why not? | ||

=Problem #2= | =Problem #2= | ||

Latest revision as of 16:06, 3 February 2011

--D. Thiebaut 15:40, 3 February 2011 (EST)

This assignment deals with minterms, Maxterms, Nands and Nors. You can work on this assignment in pairs. The due date is Friday 2/11 at midnight.

Contents

Problem #1

- Question 1

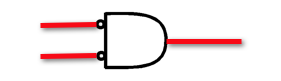

- Is the gate below a universal gate? It is an AND gate that inverts its input. If a and b are on the other side of the left red wires, the output will be not a and not b.

- Make sure you explain why this gate is, or is not, a universal gate. A simple yes or no answer will not get any credit!

- Question 2

- Is the XOR gate (Y =a'.b + a.b' ) a universal gate? Why or why not?

Problem #2

- Question 1

Implement the circuit of Homework #1 with NANDs only. One way to do so is to figure out a way to rewrite the expression for the circuit is such a way that it is a combination of terms of the form not( X and Y ):

_____ X . Y

Problem #3

- Question 1

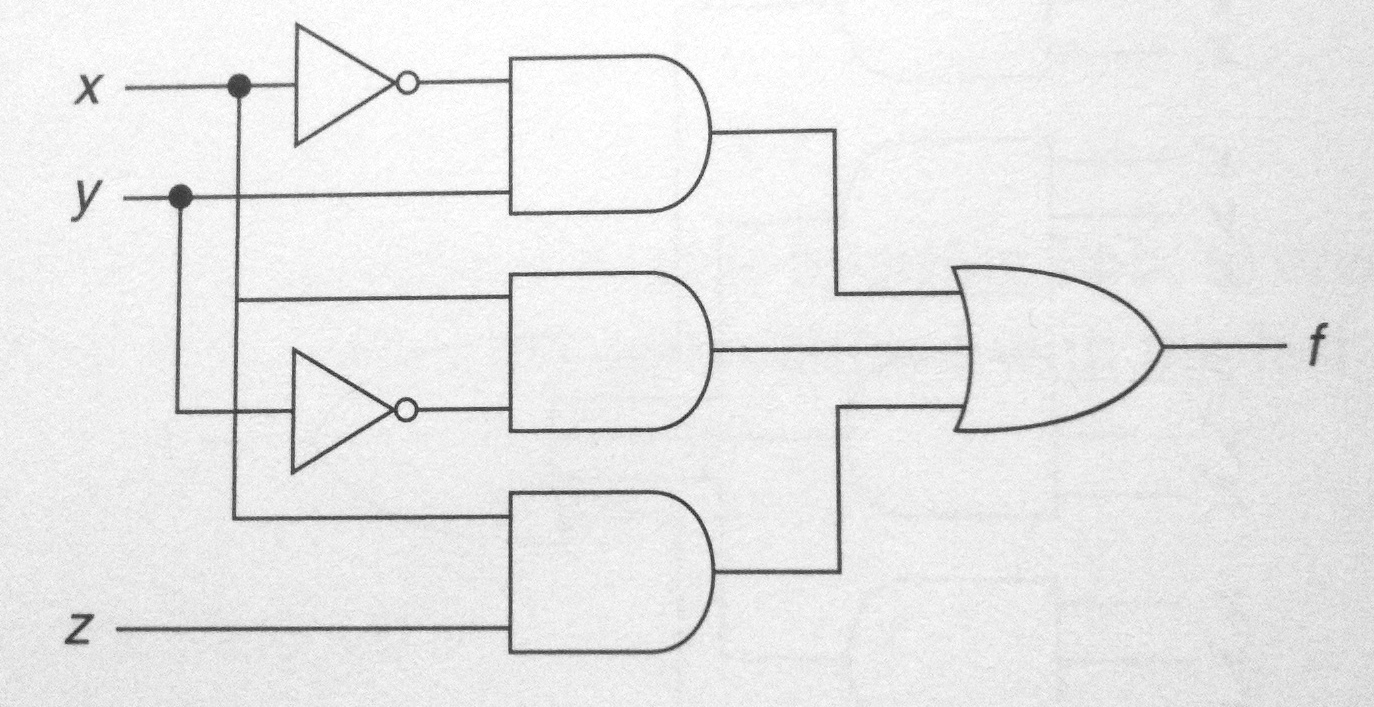

- What is the function Q( A, B, C ) implemented by the circuit shown above, where the gates are NAND gates ?

- Question 2

- What is the diagram of Q using only NOT, OR, and AND gates?

- Question 3

- What is the minterm canonical form of Q?

- Question 4

- What is its Maxterm canonical form?

Submission

- Store your answers in a pdf called hw2.pdf that you can rsync to your 270b-xx account. Once in your account, simply submit it as follows:

rsubmit hw2 hw2.pdf

- Note: if you are experiencing problem with the transfer to your account, then email me your file. In this case, call your file 270b-xx_hw2.pdf, please, where you will replace xx with your account number.