Difference between revisions of "Xilinx ISE Lab 2: Intro to Verilog"

(→New Project) |

(→New Source) |

||

| Line 112: | Line 112: | ||

</source> | </source> | ||

| + | <br /> | ||

| + | <br /> | ||

* Edit the ''Verilog'' file, and add just to lines: | * Edit the ''Verilog'' file, and add just to lines: | ||

Revision as of 15:43, 16 April 2012

--D. Thiebaut 16:37, 16 April 2012 (EDT)

This lab is the second lab introducing the Xilinx ISE and to the CoolRunner-II kit. Make sure you do Lab #1 of this series first.

This lab will show you how to create a two-bit adder in Verilog and check its correct operation with the ISim simulator.

Contents

Introduction

Xilinx's ISE is "Xilinx ISE[1] is a software tool produced by Xilinx for synthesis and analysis of HDL designs, which enables the developer to synthesize ("compile") their designs, perform timing analysis, examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer." [1]

The goal of this lab/tutorial is to get the reader familiar with the process of designing a simple digital electronic circuit, compiling it, and verifying it correct behavior with a simulator.

Knowledge of digital logic (basic gates, flip-flops, Moore machines) is assumed.

This lab is based on the excellent series of labs created for the CoolRunner CPLD by Tiffany Liu in her Independent Study in the CS. Dept. at Smith College.[2]

Lab 2: Creating a 2-bit Adder in Verilog

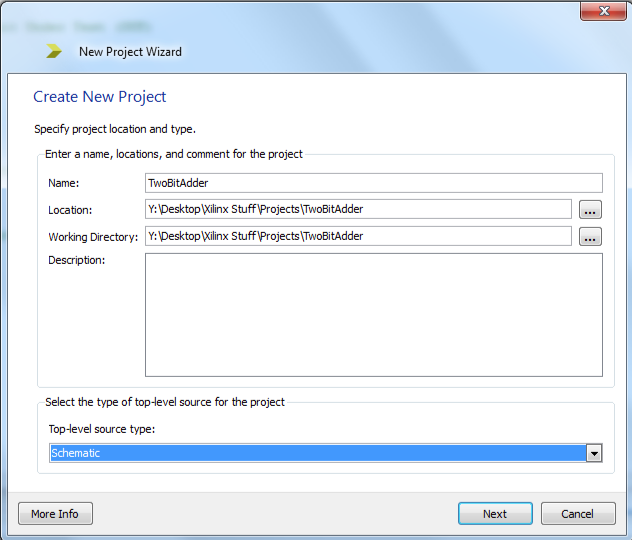

New Project

- Open the ISE

- File/New Project

- Pick a name: TwoBitAdderV

- Accept the default location

- Top-Level source: HDL

- Project Settings:

- Family: CoolRunner2 CPLDs

- Device: XC2C257 (this is the marking on the CPLD on the actual kit)

- Package: TQ144 (also marked on the CPLD on the actual kit)

- Speed: -7

- Keep all others unchanged.

New Source

- Click on top left icon (see image to the right) to add a new source to the project.

- Pick Verilog Module as the type

- Name it with a name that makes sense, e.g. circuit2.

- in the Define Module window, add A and B as inputs, and Sum and Carry as outputs.

- Finish

- You should then see the following template ready for you to complete:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 16:36:46 04/16/2012

// Design Name:

// Module Name: circuit2

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module circuit2(

input A,

input B,

output Carry,

output Sum

);

endmodule

- Edit the Verilog file, and add just to lines:

module circuit2(

input A,

input B,

output Carry,

output Sum

);

and( Carry, A, B );

xor( Sum, A, B );

endmodule

- Add wires between the inputs of the two gates (two vertical wires in the shape of [ brackets)

- Add two horizontal writes between the wires just inserted and points that will become input tags.

- Add two input tags to the two input wires just addes, and two output tags to the two outputs of the gates.

- Right-click on the Tabs and rename the two input ones as A and B, and the two output ones as Carry and Sum.

- Type Control-S to save the schematics to file.

Implementation Constraints File

The purpose of the Implementation Constraints File (ICF) is to associate input and output tabs with actual pins of the CPLD chip we are using.

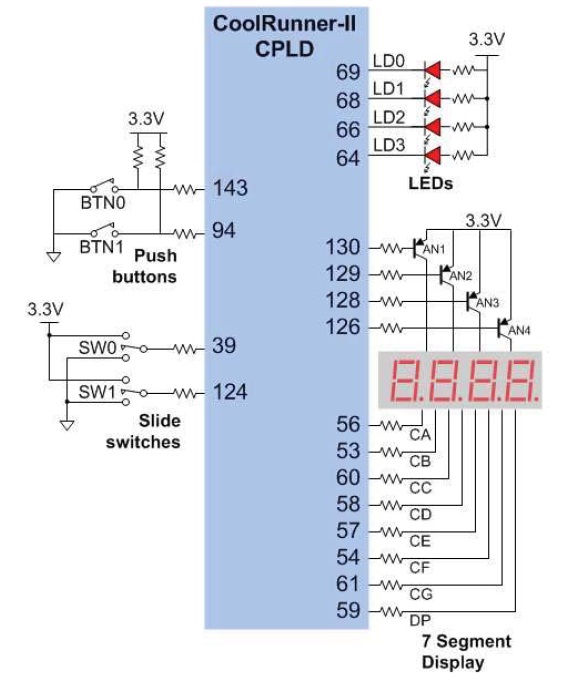

The image below shows all the pins available to us:

Note that we can use Pins 64, 66, 68, and 69 for LED outputs, and pins 39, 94, 124 and 143 for input pins.

- Click on the Design tab of the left window.

- Select the circuit1.sch file and right click on it.

- New Source. Pick Implementation Constraints File. Name it something like circuits as well. (It will get its own extension.)

- Check under the circuit1.sch menu item, there should now be a file called circuit1.ucf.

- Select the ucf file and in the lower pane (processes pane), open the User Constraints option and click on Edit Constraints.

- In the editor window on the right, enter the following lines:

NET A LOC = P124; NET B LOC = P38; NET Carry LOC = P68; NET Sum LOC = P69;

- Save with Control S

Implement Design

It is now time to

- Synthesize

- Translate

- Fit the design to the chip, and

- Generate the Programming File that can be downloaded to the device.

- Select the circuit1.sch file in the Hierarchy window

- In the Process window, double click on Implement Desgin. This will automatically call all the actions listed above. The result is a programming file that will appear in the TwoBitAdder project directory.

Downloading to the CPLD

- Unfortunately, we have to skip this step at this time as the CPLD Windows Utility that interfaces with the CPLD and allows downloading of programming file does not work under Windows 7. Only Windows XP is supported at this time (April 2012).

Testing the design with the simulator

This step will allow you to create a module that will make A and B take all the possible values ranging from 00, 01, 10, to 11, and see how the two-bit adder circuit reacts to it.

- First create a new simulation module: From the main menu, pick Project then New Source.

- Choose Verilog Test Fixture as the type of the module. Give it a meaningful name, for example test.

- Click Next and make sure that your original schematic module is selected.

- Next then Finish.

- the ISE will have generated a test module for us. It's almost what we need. We just need to modify it a tad, as shown below:

// Verilog test fixture created from schematic [...] - Mon Apr 16 14:48:13 2012

`timescale 1ns / 1ps

module circuit1_circuit1_sch_tb();

// Inputs

reg B;

reg A;

// Output

wire Carry;

wire Sum;

// Bidirs

// Instantiate the UUT

circuit1 UUT (

.Carry(Carry),

.Sum(Sum),

.B(B),

.A(A)

);

// Initialize Inputs

initial begin

B = 0;

A = 0;

// wait 100 ns

#100;

// after 10 ns, set B to 1

#10 B = 1;

// after 10 ns, set A to 1, reset B to 0

#10 A = 1;

B = 0;

// after 10 ns, set B to 1

#10 B = 1;

end

endmodule

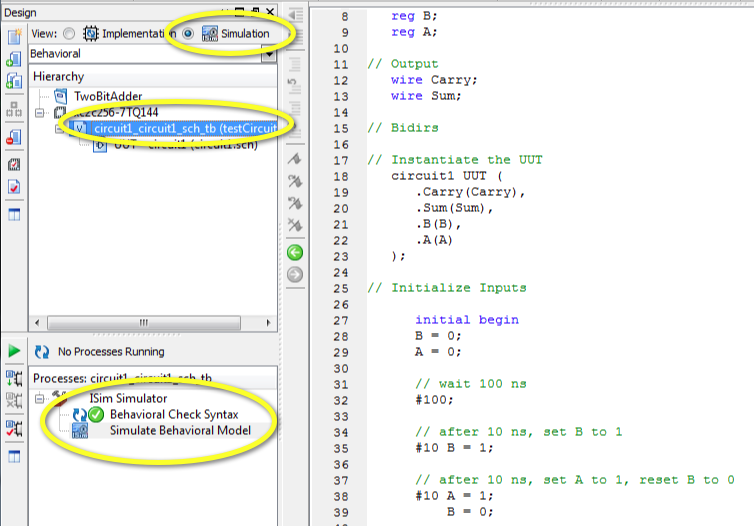

- Click on the Simulation button on top of the Hierarchy pane.

- The ISim Simulator should appear in the Process pane, below.

- Double click on Behavioral Check Syntax

- Then, assuming the process completed successfully, double click on Simulate Behavioral Model

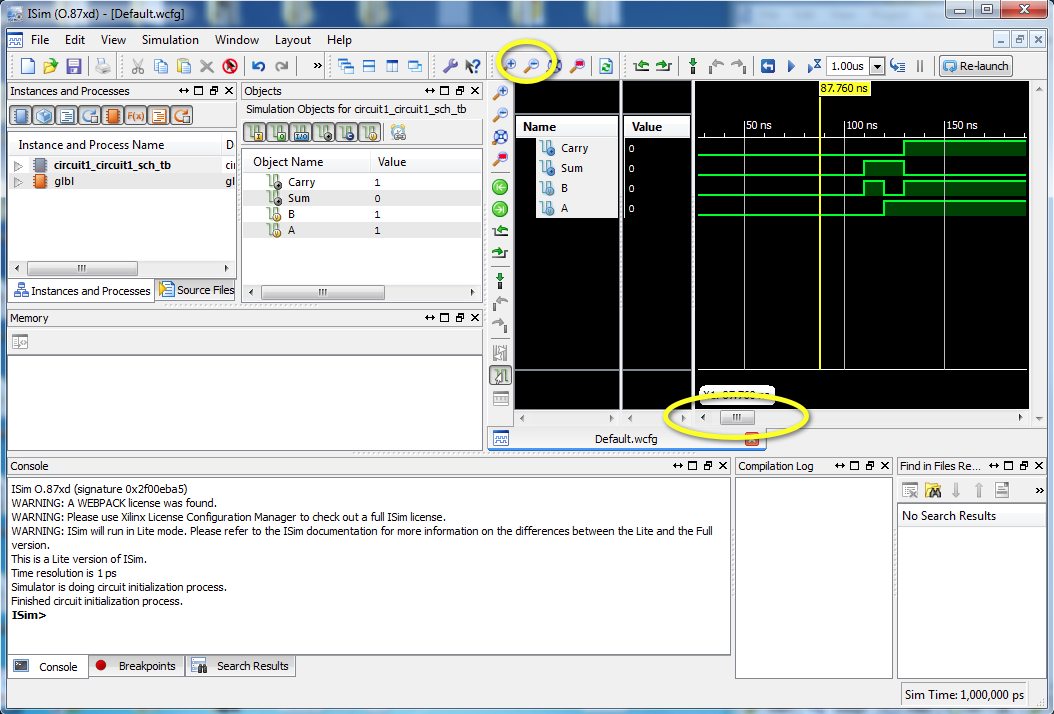

- A new window should open up, presenting a timing diagram. Use slider and the magnifying glass + and - icons to zoom in on the marker at Time 100ns, and see how Sum and Carry react to the changing A and B signals.

- Make sure you verify that the adder works correctly.

Challenge #1 |

- Use the same approach illustrated here and create a 3-bit adder.

References

- ↑ Xilinx ISE, captured on wikipedia.org, April 2012.

- ↑ Tiffany Liu, CSC270 Labs on the CoolRunner-II, Independent Study, Fall 2011, cs.smith.edu/classwiki.