Difference between revisions of "CSC270 Lab 6 2011"

(→1-Flipflop Sequencer/Oscillator) |

(→Machine 1) |

||

| (8 intermediate revisions by the same user not shown) | |||

| Line 7: | Line 7: | ||

=LAB #6: The 74LS74 D-Flip-Flop= | =LAB #6: The 74LS74 D-Flip-Flop= | ||

| + | |||

| + | <font color="magenta">(This part should have already been done last week and is reported here for completeness)</font> | ||

The [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls74arev5.pdf 74LS74] chip contains two flip-flops: | The [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls74arev5.pdf 74LS74] chip contains two flip-flops: | ||

| Line 46: | Line 48: | ||

=1-Flipflop Sequencer/Oscillator= | =1-Flipflop Sequencer/Oscillator= | ||

| − | Implement the circuit below: | + | * Implement the circuit below: |

<center>[[Image:CSC270_oscillator.png | 500px ]] </center> | <center>[[Image:CSC270_oscillator.png | 500px ]] </center> | ||

| − | Connect both the Clock and Q signals to logic indicators. | + | * Connect both the Clock and Q signals to logic indicators. Set the Clock to 1 Hz. |

| + | |||

| + | * Connect CLR and PR to 1. | ||

* What is the frequency at which the Q output oscillates? | * What is the frequency at which the Q output oscillates? | ||

| + | |||

| + | * Now set the clock frequency to 100 KHz (100,000 Hertz) and observe Clock and Q on the scope. | ||

* What is the relationship between the frequency of Q and the frequency of the clock input? Does the 74LS74 wired this way behave as a frequency multiplier or a frequency divider? | * What is the relationship between the frequency of Q and the frequency of the clock input? Does the 74LS74 wired this way behave as a frequency multiplier or a frequency divider? | ||

| Line 58: | Line 64: | ||

* Draw the state diagram of this finite-state machine (FSM). | * Draw the state diagram of this finite-state machine (FSM). | ||

| − | * Implement and wire-up a divide-by-4 frequency divider. Demonstrate that | + | * Implement and wire-up a divide-by-4 frequency divider. Make the scope show the frequency of your signals. Demonstrate that your divider works! |

| + | =2-bit Flip-flop Sequencers= | ||

| − | + | * For these two machines, bring the Clock frequency to 1 Hz and observe the behavior of the outputs on the LED display. | |

==Machine 1== | ==Machine 1== | ||

| − | * Build a state-machine with 2 flip-flops. Flip-flop 1 has input D1 and outputs Q1 and Q1'. Flip-flop | + | * Build a state-machine with 2 flip-flops. Flip-flop 1 has input D1 and outputs Q1 and Q1'. Flip-flop 0 has input D0 and outputs Q0 and Q0'. |

* Perform the following connections. | * Perform the following connections. | ||

| Line 70: | Line 77: | ||

** D0 = Q1 NOR Q0 | ** D0 = Q1 NOR Q0 | ||

** Connect the Pr1, Pr0 inputs to a momentary switch with a default high level. | ** Connect the Pr1, Pr0 inputs to a momentary switch with a default high level. | ||

| − | ** Connect the | + | ** Connect the Clr1, Clr0 inputs to another momentary switch with a default high level. |

** Connect the two clock signals to the 1 Hz clock signal. | ** Connect the two clock signals to the 1 Hz clock signal. | ||

** Connect Q0 and Q1 to two LEDs | ** Connect Q0 and Q1 to two LEDs | ||

| Line 83: | Line 90: | ||

: Again, how many different states does your machine have? | : Again, how many different states does your machine have? | ||

| − | + | ==Machine 2 (optional)== | |

| − | ==Machine 2 ( | ||

* Change the connections so that the equations for D1 and D0 become: | * Change the connections so that the equations for D1 and D0 become: | ||

** D1 = Q0 | ** D1 = Q0 | ||

| Line 97: | Line 103: | ||

: Again, how many different states does your machine have? | : Again, how many different states does your machine have? | ||

<br /> | <br /> | ||

| + | |||

| + | =FSM with output= | ||

| + | |||

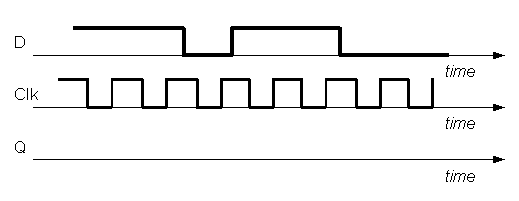

| + | * Take one of Machine 1 or Machine 2 above, and use its two Q outputs to generate a signal that is 1 for 1 period of time, and 0 for two. | ||

| + | |||

| + | <br /> | ||

| + | <center>[[Image:CSC270TimingDiagram3States.png|350px]]</center> | ||

<br /> | <br /> | ||

Latest revision as of 17:03, 28 February 2011

--D. Thiebaut 22:58, 27 February 2011 (EST)

Contents

LAB #6: The 74LS74 D-Flip-Flop

(This part should have already been done last week and is reported here for completeness)

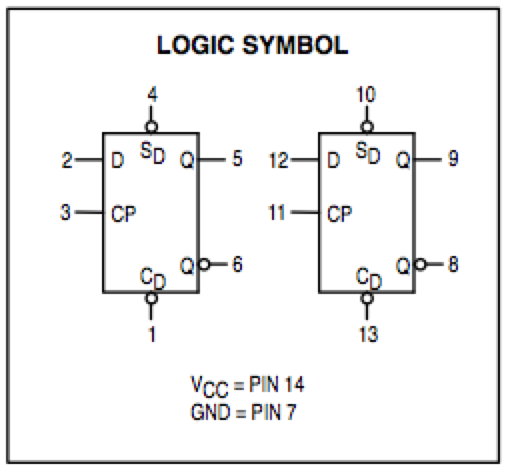

The 74LS74 chip contains two flip-flops:

- Put one on your bread board, and connect Preset and Clear to two switches, D to another switch, and Clock to the 1Hz clock signal.

- Set both Preset and Clear to 1.

- Connect D, Clock, Q, and Q-bar to 4 LEDs.

- Slowly change the D input from low to high and observe how the signals change.

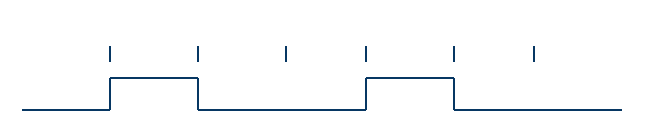

- From your observations, complete the timing diagram below so that we can see how Q and Q-bar change, according to your observations, not to what you think should happen.

Clear active

Same question, but this time you will set the Clear input to 0.

Preset active

Same question, but this time you will set the Preset input to 0 (and return Clear to 1).

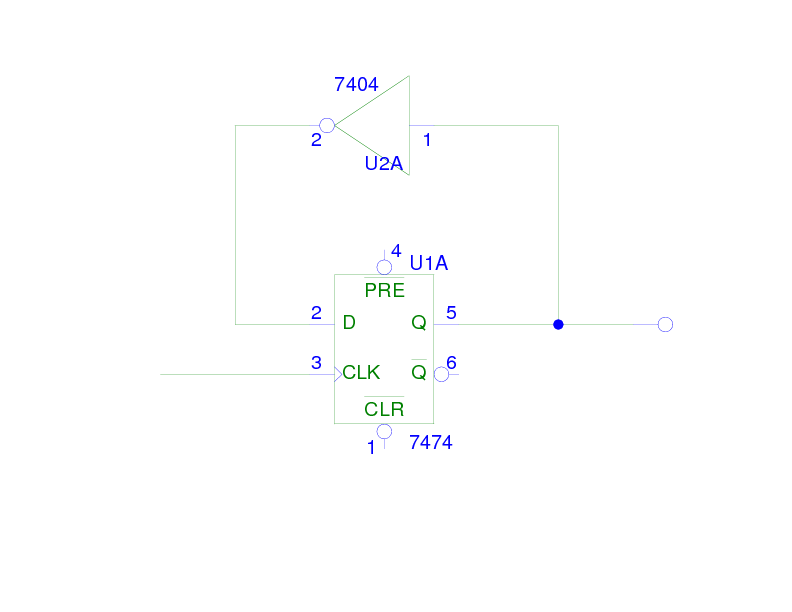

1-Flipflop Sequencer/Oscillator

- Implement the circuit below:

- Connect both the Clock and Q signals to logic indicators. Set the Clock to 1 Hz.

- Connect CLR and PR to 1.

- What is the frequency at which the Q output oscillates?

- Now set the clock frequency to 100 KHz (100,000 Hertz) and observe Clock and Q on the scope.

- What is the relationship between the frequency of Q and the frequency of the clock input? Does the 74LS74 wired this way behave as a frequency multiplier or a frequency divider?

- Draw the state diagram of this finite-state machine (FSM).

- Implement and wire-up a divide-by-4 frequency divider. Make the scope show the frequency of your signals. Demonstrate that your divider works!

2-bit Flip-flop Sequencers

- For these two machines, bring the Clock frequency to 1 Hz and observe the behavior of the outputs on the LED display.

Machine 1

- Build a state-machine with 2 flip-flops. Flip-flop 1 has input D1 and outputs Q1 and Q1'. Flip-flop 0 has input D0 and outputs Q0 and Q0'.

- Perform the following connections.

- D1 = Q0

- D0 = Q1 NOR Q0

- Connect the Pr1, Pr0 inputs to a momentary switch with a default high level.

- Connect the Clr1, Clr0 inputs to another momentary switch with a default high level.

- Connect the two clock signals to the 1 Hz clock signal.

- Connect Q0 and Q1 to two LEDs

- Question 1

- How many states does your machine have?

- Question 2

- Activate the momentary switch that is connected to the Preset inputs. What happens with Q1 and Q0

- Question 3

- Again, how many different states does your machine have?

Machine 2 (optional)

- Change the connections so that the equations for D1 and D0 become:

- D1 = Q0

- D0 = NOT ( Q1 XOR Q0 )

- Question 1

- How many states does your machine have?

- Question 2

- Activate the momentary switch that is connected to the Preset inputs. What happens with Q1 and Q0

- Question 3

- Again, how many different states does your machine have?

FSM with output

- Take one of Machine 1 or Machine 2 above, and use its two Q outputs to generate a signal that is 1 for 1 period of time, and 0 for two.