CSC270 Lab 6 2011

Revision as of 22:58, 27 February 2011 by Thiebaut (talk | contribs) (Created page with "--~~~~ Back to the weekly schedule <br />--D. Thiebaut 13:25, 25 February 2009 (UTC) ---- __TOC__ <br /> <br /> =LAB #6: The 74LS74 D-F...")

--D. Thiebaut 22:58, 27 February 2011 (EST) Back to the weekly schedule

--D. Thiebaut 13:25, 25 February 2009 (UTC)

Contents

LAB #6: The 74LS74 D-Flip-Flop

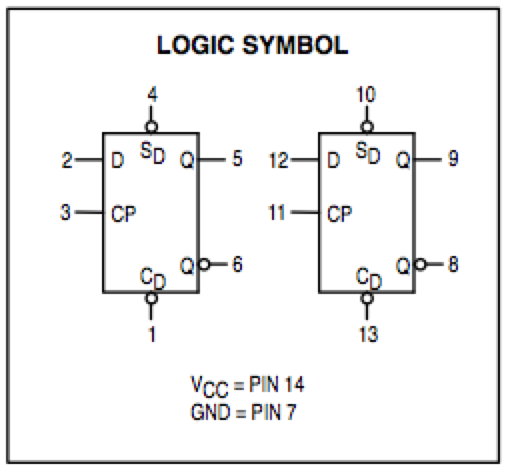

The 74LS74 chip contains two flip-flops:

- Put one on your bread board, and connect Preset and Clear to two switches, D to another switch, and Clock to the 1Hz clock signal.

- Set both Preset and Clear to 1.

- Connect D, Clock, Q, and Q-bar to 4 LEDs.

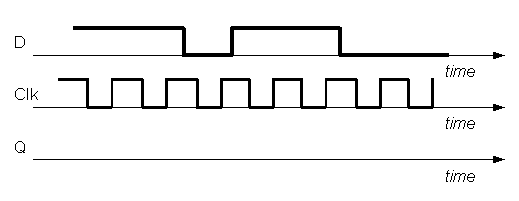

- Slowly change the D input from low to high and observe how the signals change.

- From your observations, complete the timing diagram below so that we can see how Q and Q-bar change, according to your observations, not to what you think should happen.

Clear active

Same question, but this time you will set the Clear input to 0.

Preset active

Same question, but this time you will set the Preset input to 0 (and return Clear to 1).

1-Flipflop Sequencer/Oscillator

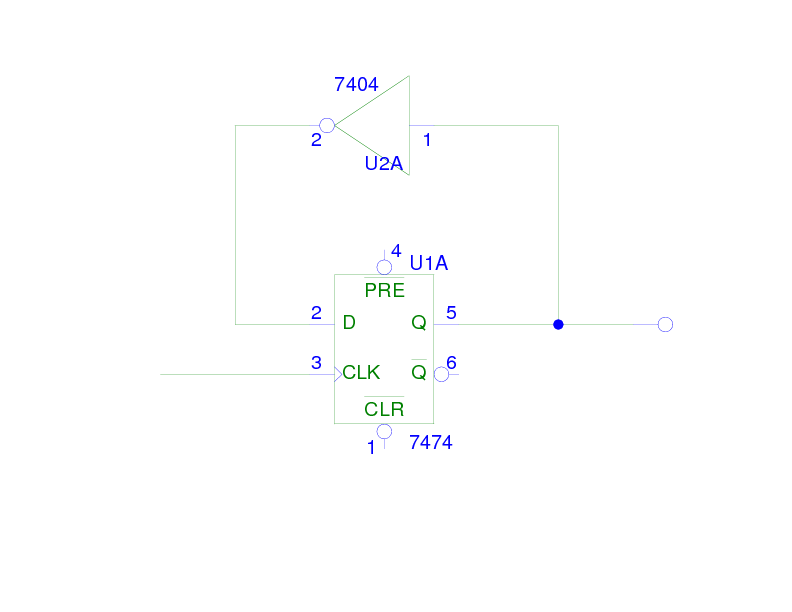

Implement the circuit below:

Connect both the Clock and Q signals to logic indicators.

- What is the frequency at which the Q output oscillates?

- What is the relationship between the frequency of Q and the frequency of the clock input? Does the 74LS74 wired this way behave as a frequency multiplier or a frequency divider?

- Draw the state diagram of this finite-state machine (FSM).

- Implement and wire-up a divide-by-4 frequency divider. Demonstrate that it works!