CSC103 Exercise: Functional Description to Logic Design

--D. Thiebaut 22:12, 7 February 2012 (EST)

This exercise illustrates the process of going from the formulation of a problem to the design of a solution that involves AND, OR and NOT logic circuits.

The Problem

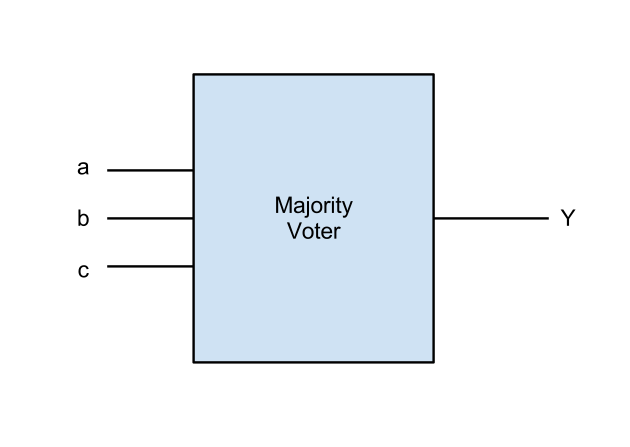

Create a circuit made of AND, OR, and NOT gates that computes the majority of three bits.

- Question 1

- Generate the truth table for this circuit

- Question 2

- Generate the boolean expression for the output signal

- Question 3

- Translate the equation into a logic circuit with AND, OR, and NOT gates

- Question 4

- How could you verify that your circuit is accurate?