Difference between revisions of "CSC270 Class Page 2009"

(→Weekly Schedule) |

(→Motorola 68HC11 Documentation) |

||

| (135 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

| − | + | [[CSC270 | Back]] to Main Page for CSC270 | |

| − | =Prof= | + | ---- |

| + | __TOC__ | ||

| + | |||

| + | <center> | ||

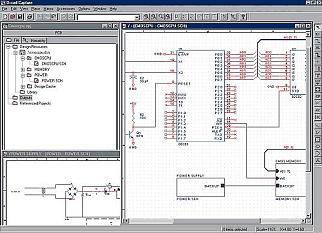

| + | [[Image:cant_sleep.png | 700px]] | ||

| + | <br>From [http://xkcd.org/571/ xkcd] | ||

| + | </center> | ||

| + | |||

| + | =Prof and TA= | ||

{| | {| | ||

| width="100%" | | | width="100%" | | ||

| Line 9: | Line 17: | ||

Office hours MW 10:30-12:00, W 1-3, and by appointments | Office hours MW 10:30-12:00, W 1-3, and by appointments | ||

|} | |} | ||

| + | |||

| + | <br /> | ||

| + | The TA for the class is Lei Lei, and her hours and location are available [http://tango.csc.smith.edu/classwiki/index.php/CSC270_TA_Hours here] | ||

=Weekly Schedule= | =Weekly Schedule= | ||

| − | + | <onlysmith> | |

{| style="width:100%" border="1" | {| style="width:100%" border="1" | ||

|- style="background:#ffdead;" | |- style="background:#ffdead;" | ||

| Line 20: | Line 31: | ||

|width="15%"| Week 1 <br /> 1/26 | |width="15%"| Week 1 <br /> 1/26 | ||

|width="60%"| | |width="60%"| | ||

| − | * | + | |

| + | * '''Monday''': Introduction to the semester | ||

| + | ** Syllabus | ||

| + | ** Overview of the class | ||

| + | ** combinational logic (1/4) | ||

| + | ** sequential logic( 1/4) | ||

| + | ** microprocessor logic (1/2) | ||

| + | ** [http://en.wikipedia.org/wiki/Boolean_algebra_(structure) Boolean Algebra] | ||

| + | ** Truth tables | ||

| + | ** Boolean functions | ||

| + | * '''Wednesday''': | ||

| + | ** boolean functions | ||

| + | ** canonical forms: the minterm canonical form | ||

| + | ** exercises | ||

| + | ** examples of [http://klabs.org/history/ech/agc_schematics/index.htm schematics] from Nasa | ||

| + | ** logic gates | ||

| + | *** and gate (7408) | ||

| + | *** or gate (7432) | ||

| + | *** not gate (7404) | ||

---- | ---- | ||

* [[CSC270_Lab_1 | Lab #1 ]] | * [[CSC270_Lab_1 | Lab #1 ]] | ||

| − | * [[CSC270_Homework_1 | Homework #1]] | + | * [[CSC270_Homework_1 | Homework #1]] and [[CSC270_Homework_1_Solutions | solution]] |

|| | || | ||

| − | + | * Binary numbers | |

| + | * Boolean algebra and Logic Gates | ||

| + | * Basic theorems | ||

| + | * Truth tables | ||

| + | * Boolean functions | ||

| + | * Canonical forms | ||

| + | <br/>[[Image:Boole visu.jpg| 150px|George Boole in zeros and ones]] | ||

| + | <br/>George Boole | ||

<!-- ================================================================== --> | <!-- ================================================================== --> | ||

| Line 32: | Line 68: | ||

| Week 2 <br /> 2/2 | | Week 2 <br /> 2/2 | ||

|| | || | ||

| − | * | + | * '''Monday''' |

| + | ** Maxterm [http://en.wikipedia.org/wiki/Canonical_form_(Boolean_algebra) canonical form] | ||

| + | ** NAND and NOR gates | ||

| + | * '''Wednesday''' | ||

| + | ** [[CSC270_GenerateTruthTable.py | Python program]] to generate a truth table | ||

| + | ** A fully developed example: a majority voter, with 3 inputs, a Majority output, a Fault output, and two Id outputs identifying the faulty input. | ||

| + | ** Introduction to [http://en.wikipedia.org/wiki/Karnaugh_map Karnaugh Maps] | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_2 | Lab #2 ]] | |

| − | * | + | * [[CSC270_Homework_2 | Homework #2]] and [[CSC270_Homework_2_Solution | Solution]] |

|| | || | ||

| − | * | + | * Canonical Forms |

| − | + | * Universal gates: NAND and NOR | |

<!-- ================================================================== --> | <!-- ================================================================== --> | ||

|- style="background:#ffffff" valign="top" | |- style="background:#ffffff" valign="top" | ||

| Week 3 <br /> 2/9 | | Week 3 <br /> 2/9 | ||

|| | || | ||

| − | * | + | [[Image:CS270_memory_die.jpg | right | 200px|Die of a memory chip]] |

| + | * '''Monday''' | ||

| + | ** Tips and Tricks: counting the number of inversions on a signal path | ||

| + | ** MSI: medium scale integration | ||

| + | *** decoders | ||

| + | *** '''active-low''' and '''active-high''' signals | ||

| + | *** The [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls42rev5.pdf 74LS42] decoder | ||

| + | *** Animated [http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/10-gates/40-mux-demux/demo74154.html 74154] decoder | ||

| + | *** Cascading decoders | ||

| + | *** multiplexers | ||

| + | *** Animated [http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/10-gates/40-mux-demux/mux21-mux41.html multiplexer] | ||

| + | * '''Wednesday''' | ||

| + | ** Do-it-yourself decoder: with/without enable, active-high/active-low signals | ||

| + | ** More decoder cascading | ||

| + | ** Multiplexers (mux) | ||

| + | ** Simplifying functions with multiplexers | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_3 | Lab #3 ]] | |

| − | * | + | * [[CSC270_Homework_3 | Homework #3]] and [[CSC270_Homework_3_Solutions | solutions]] |

|| | || | ||

| − | * | + | * Medium scale integration |

| + | * The decoder | ||

| + | * The multiplexer | ||

| + | * Simplifying circuits with decoders or multiplexers | ||

| Line 55: | Line 115: | ||

| Week 4 <br /> 2/16 | | Week 4 <br /> 2/16 | ||

|| | || | ||

| − | * | + | * '''Monday 2/16''': |

| + | ** Timing diagrams and combinational circuits | ||

| + | ** the concepts of ''blocking'' and ''passing'' gates | ||

| + | ** Meeting the RS flip-flop | ||

| + | ** A single-input RS flip-flop | ||

| + | ** A single-input, pulsed RS flip-flop | ||

| + | ** The two-stage D flip-flop | ||

| + | ** understanding the D flip-flop | ||

| + | ** the [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls74arev5.pdf 74LS74] datasheet | ||

| + | ** Exercises | ||

| + | * 2/18 <font color="purple">'''Rally Day'''</font>, No Class | ||

---- | ---- | ||

* | * | ||

|| | || | ||

| − | * | + | * Sequential circuits |

| + | * RS Flip-flop | ||

| + | * D Flip-flop | ||

<!-- ================================================================== --> | <!-- ================================================================== --> | ||

| Line 66: | Line 138: | ||

| Week 5 <br /> 2/23 | | Week 5 <br /> 2/23 | ||

|| | || | ||

| − | * | + | * '''Monday''' |

| + | ** The D-flip-flop explained (Movie available on [http://www.youtube.com/watch?v=tctj9lmEEZc YouTube]!) | ||

| + | ** A simple GYR sequencer | ||

| + | * '''Wednesday''' | ||

| + | ** Continuation of the GYR sequencer | ||

| + | ** Let's not forget decoders! | ||

| + | ** Debouncing switches and clock signals | ||

| + | ** Python to the rescue! A [[CSC270_GYRSequencer.py | program]] to simulate a sequencer | ||

| + | ** Exercises | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_4 | Lab #4 ]] | |

| − | * | + | * [[CSC270_Homework_4 | Homework #4]] and [[CSC270_Homework_4_Solution | Solution]] |

|| | || | ||

* | * | ||

| Line 77: | Line 157: | ||

|- style="background:#eeeeff" valign="top" | |- style="background:#eeeeff" valign="top" | ||

| Week 6 <br /> 3/2 | | Week 6 <br /> 3/2 | ||

| − | || | + | || |

| − | * | + | [[Image:calvin_snow.jpg | 150px | right ]] |

| + | [[Image:CSC270_JKFlipflop.jpg | 250px | right]] | ||

| + | * '''Monday''': Snow Day | ||

| + | |||

| + | * '''Wednesday''': | ||

| + | ** Analysis: behavior of a 2-bit sequencer with equations D1 = Q1^Q0, D0=Q1'. | ||

| + | ** Random start, and forced reset | ||

| + | ** A GYR sequencer with an outside input signal. | ||

| + | ** Exercise | ||

| + | ** JK Flipflop | ||

| + | <br /> | ||

| + | <br /> | ||

| + | <br /> | ||

| + | <br /> | ||

| + | <br /> | ||

| + | <br /> | ||

| + | <br /> | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_5 | Lab #5 ]] | |

| − | * | + | * [[CSC270_Homework_5 | Homework #5]] and [[CSC270_Homework_5_Solution | Solution]] |

|| | || | ||

| − | * | + | * Sequencers with outside controls |

| − | + | * The JK flipflop | |

| + | * Building sequencers with JK flipflops | ||

<!-- ================================================================== --> | <!-- ================================================================== --> | ||

|- style="background:#ffffff" valign="top" | |- style="background:#ffffff" valign="top" | ||

| Week 7 <br /> 3/9 | | Week 7 <br /> 3/9 | ||

|| | || | ||

| − | * | + | * '''<font color="purple">3/11 Midterm Exam</font>''' |

| + | * [[Media:midtermPrep.pdf | Midterm Preparation]] (Note that in Question 5 the Inputs should be labeled I0, I1, and I2. 0 is connected to I2, which is the MSB) | ||

---- | ---- | ||

| Line 101: | Line 199: | ||

| Week 8 <br /> 3/16 | | Week 8 <br /> 3/16 | ||

|| | || | ||

| − | + | ||

| + | <center>[[Image:dancingCalving.gif ]]</center> | ||

|| | || | ||

| | ||

| Line 109: | Line 208: | ||

| Week 9 <br /> 3/23 | | Week 9 <br /> 3/23 | ||

|| | || | ||

| − | * & | + | [[Image:6811Motorola.jpg | 200px | right]] |

| + | |||

| + | * '''Monday:''' | ||

| + | **The 6811 Processor: references | ||

| + | *** The official Motorola [http://maven.smith.edu/~thiebaut/classes/270/6811/68hc11a8.pdf 68HC11A8 Data Sheet]. Fairly cryptic... | ||

| + | *** A Motorola [[Media:6811Manual.pdf | 6811 Manual]]. It is a nicely written refresher on many concepts of assembly language applied to the 6811. | ||

| + | **** Check Section 3.2 on addressing modes (inherent, direct, extended, indexed, relative). | ||

| + | **** Get a refresher for the different instruction types (arithmetic, shifts, control, etc) in Section 3.4. | ||

| + | **** The condition code register is covered in Section 3.5. Skip Section 4. | ||

| + | *** [http://maven.smith.edu/~thiebaut/classes/270/6811/68hc11ref-2002.pdf M68HC11 Technical Reference], from Motorola. | ||

| + | ****Section 6.5 shows the instructions in logical groups. | ||

| + | ** [http://maven.smith.edu/~thiebaut/classes/270/6811/68hc11pocket.pdf M68HC11 Pocket Reference]. | ||

| + | ***Very useful, on Page 15, a list of all the opcodes supported by the 6811, in numerical (hex) order. | ||

| + | ** [http://maven.smith.edu/~thiebaut/classes/270/6811/68hc11a8ref.pdf 68HC11A8 Technical Reference]: a hardware & engineering description. of the 6811, its ports, and how it operates. | ||

| + | **** See Section 10 for a cycle-by-cycle description of the execution of each instruction. | ||

| + | **** See Appendix A, Figure A-14 for the timing diagram of a typical (multiplexed expansion) memory access. | ||

| + | ** [http://www.ele.uri.edu/Courses/ele205/6811-Instructions/index.html 6811 Instruction Set], with hexadecimal opcodes. A reverse map, from hex to instructions can be found [http://home.earthlink.net/~tdickens/68hc11/68hc11_opcode_map.html here.] | ||

| + | ** [[Media:CSC270_Assembly_Instructions.pdf | 2-Page List]] of all the 6811 Instructions | ||

| + | ** [http://www.aspisys.com/asm11.htm Software] for the 6811 | ||

| + | * '''Wednesday:''' | ||

| + | ** Concentration on Assembly Language | ||

| + | ** [[Image:CSC270_6811_Listing_Format.png | 200 px | right ]] Listing format | ||

| + | *** opcodes, mnemonics, directives, columnar format | ||

| + | ** The instructions | ||

| + | ** Addressing Modes: inherent, immediate, direct, extended, indexed, relative | ||

| + | ** Exercises, exercises, exercises!!! | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_6 | Lab #6 ]] | |

| − | * | + | * [[CSC270_Homework_7 | Homework #7]] |

| − | || | + | || |

| − | * | + | *Read the [[Media:6811Manual.pdf |6811 Manual ]] for this week. Quiz on Monday 3/30/09 on this material. |

| + | *[http://maven.smith.edu/~thiebaut/classes/231_0708/crashcourse/ Crash course] on Assembly Language | ||

| Line 121: | Line 246: | ||

| Week 10 <br /> 3/30 | | Week 10 <br /> 3/30 | ||

|| | || | ||

| − | * & | + | * '''Monday:''' |

| + | ** Quiz on the information in [[Media:6811Manual.pdf |6811 Manual ]] (You can skip Section 4) | ||

| + | ** Timing Diagrams: conventions (transitions, floating signals, unknown, propagation times) | ||

| + | ** The E and R/W' signals (see the Google book [http://books.google.com/books?id=TcxukvTzxBcC&pg=PA435&lpg=PA435&dq=6811+timing+read+write+clock&source=bl&ots=XwSUe1MtSY&sig=dAOl2Ktzk58xsVCz4i6ARogMNcY&hl=en&ei=LqbQScOpIaLrlQfA55HWCQ&sa=X&oi=book_result&resnum=4&ct=result#PPA218,M1 ''MC68HC11, an introduction''] by Han-Way Huang, Section 5.7) | ||

| + | ** The timing of the execution of a 6811 instruction | ||

| + | ** the E signal | ||

| + | ** the R/W' signal | ||

| + | ** Timing of complete instructions | ||

| + | *** LDAA #3 | ||

| + | *** LDAA 03 | ||

| + | *** LDAA 0003 | ||

| + | *** LDAA 3,X | ||

| + | *** STAA 03 | ||

| + | *** STAA 0003 | ||

| + | *** STAA 3,X | ||

| + | ** Timing of a full program | ||

| + | * '''Wednesday''' | ||

| + | ** Exercise: timing of an endless loop (preparation for the lab) | ||

| + | ** The conditional branch instructions and relative addressing mode | ||

---- | ---- | ||

| + | * [[CSC270_Lab_7 | Lab #7 ]] | ||

| + | * [[CSC270_Homework_8 | Homework #8]] | ||

| − | |||

|| | || | ||

* | * | ||

| Line 132: | Line 276: | ||

| Week 11 <br /> 4/6 | | Week 11 <br /> 4/6 | ||

|| | || | ||

| − | * | + | *'''Monday''' |

| + | ** Relative Addressing | ||

| + | ** BRA, BEQ, BNE, etc. | ||

| + | ** Exercises | ||

| + | * '''Wednesday''' | ||

| + | ** Designing a 1-bit I/O output port. | ||

| + | ** Decoding the address bus | ||

| + | *** Ideal case: 1 RAM chip | ||

| + | *** Case 2: 1 RAM + 1 ROM chips covering the whole space | ||

| + | *** Case 3: 1 RAM + 1 ROM chips covering only 1/4 each of the whole address space | ||

| + | *** Case 4: Add a memory-mapped 1-bit ouput port in the unused space | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_8 | Lab #8 ]] | |

| − | * | + | * [[CSC270_Homework_9 | Homework #9]] and [[CSC270_Homework_9_Solution | Solution]] |

| − | || | + | || |

* | * | ||

| Line 144: | Line 298: | ||

| Week 12 <br /> 4/13 | | Week 12 <br /> 4/13 | ||

|| | || | ||

| − | * | + | [[Image:CSC270_74244.png | 100 px | right ]] |

| + | [[Image:CSC270_74541.png | 100 px | right ]] | ||

| + | [[Image:CSC270_74240.png | 100 px | right ]] | ||

| + | |||

| + | * '''Monday''': | ||

| + | ** [[CSC270_Lab_8_1/2 | Mini Lab]]: Two-bit port ( from [[CSC270_Lab_8#Two-bit_Port | Lab #8]]) | ||

| + | ** Generating [http://www.electronics-project-design.com/Infrared-remote-control-software.html signals] for a remotely controlled device | ||

| + | * '''Wednesday''' | ||

| + | ** Tri-state drivers | ||

| + | |||

---- | ---- | ||

| − | + | * [[CSC270_Lab_9 | Lab #9]] | |

| − | * | + | * [[CSC270_Homework_10 | Homework #10 ]] and [[CSC270_Homework_10_Solution | Solution]] |

|| | || | ||

| − | * | + | * Read the section on Tri-state buffers in Mano's textbook |

<!-- ================================================================== --> | <!-- ================================================================== --> | ||

| Line 155: | Line 318: | ||

| Week 13 <br /> 4/20 | | Week 13 <br /> 4/20 | ||

|| | || | ||

| − | * | + | [[Image:CSC270_centronics.jpg | 150px | right ]] |

| + | [[Image:CSC270_parallelPortTiming.jpg | 150px | right]] | ||

| + | * '''Monday''': The Parallel Port. Control, Status, Data registers. | ||

| + | ** Signals (see [http://www.nullmodem.com/Centronics.htm this link]) | ||

| + | ** Protocol with Strobe and Ack (see [[Media:CSC270_ParallelPort.pdf | this document]]) | ||

| + | ** Driver code for outputting a byte to a Centronics Port | ||

| + | * '''Wednesday''': the 2114 RAM | ||

| + | ** Timing requirement of the 2114 | ||

| + | ** Wiring a 2114 to a 6811 | ||

| + | ** Software testing | ||

---- | ---- | ||

| − | + | * [[CSC270_Lab_10 | Lab #10]] | |

| − | * | + | * [[CSC270_Homework_11 | Homework #11 ]] |

|| | || | ||

| − | * | + | * Parallel Port References |

| − | + | ** [http://www.nullmodem.com/Centronics.htm Signal] description | |

| + | ** [[Media:CSC270_ParallelPort.pdf | Protocol ]] | ||

| + | ** [[Media:CSC270_75574.pdf | Octal D-Flipflop]] | ||

<!-- ================================================================== --> | <!-- ================================================================== --> | ||

|- style="background:#eeeeff" valign="top" | |- style="background:#eeeeff" valign="top" | ||

| Week 14 <br /> 4/27 | | Week 14 <br /> 4/27 | ||

|| | || | ||

| − | * | + | [[Image:Sim2.jpg | right | 150 px]] |

| + | * '''Monday''': Selected Topics in Computer Architecture | ||

| + | ** [[CSC270 Exercises on Memory Configuration | Exercises]] on memory | ||

| + | ** ROM-based sequencers | ||

| + | ** Hardware simulator | ||

| + | <!--A bird's eye view of Computer Architecture. | ||

| + | ** Processors: microprogram, caches, pipeline, Branch-Prediction Table | ||

| + | ** Ports: USB | ||

| + | ** Memory: dynamic RAM--> | ||

| + | * '''Wednesday''': | ||

| + | * <font color="purple">'''1-week Take-Home Final Exam'''</font> | ||

| + | * No lab | ||

---- | ---- | ||

| − | * | + | * [[CSC270 Final Exam | Final Exam]] |

|| | || | ||

* | * | ||

| Line 175: | Line 360: | ||

|} | |} | ||

| + | </onlysmith> | ||

| + | ---- | ||

| + | [[CSC270 2009 | Back]] To Main Page | ||

| + | ---- | ||

| + | |||

| + | =Links and Resources= | ||

| + | |||

| + | ==Programs== | ||

| + | * [[CSC270 GenerateTruthTable.py | A Python program]] that generates a truth table. | ||

| + | |||

| + | ==Software== | ||

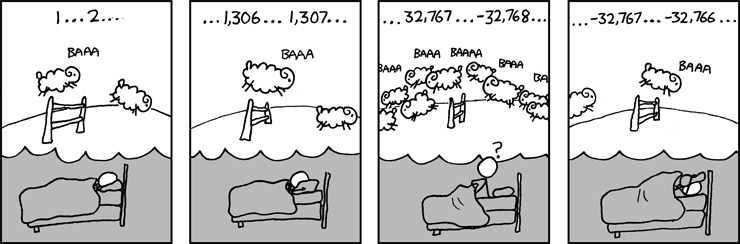

| + | [[Image:pspice9.jpg | right | 200 px]] | ||

| + | ===PSpice 9=== | ||

| + | * Pspice 9, Student version. An nice alternative to drawing schematics by hand. | ||

| + | * This is a '''Windows''' version. (I have tried to make it work under wine/Mac OS X but haven't been able to make it load the libraries correctly) | ||

| + | * Make sure you select the '''schematics''' option when installing the software. | ||

| + | * Select Tools/Schematics when starting the editor | ||

| + | * The schematics editor is located in C:\Program Files\OrCAD_Demo\PSpice\PDesign.exe upon installation. | ||

| + | * Download [http://cs.smith.edu/~thiebaut/classes/270/software/ps9_1.zip here]! | ||

| + | * PSpice [http://ewh.ieee.org/soc/es/Nov1999/02/BEGIN.HTM Tutorial] | ||

| + | |||

| + | ==Integrated Circuit Data-Sheets== | ||

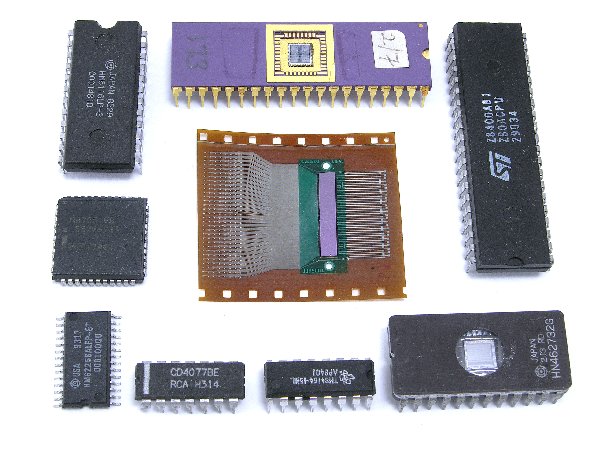

| + | [[Image:Ic.jpg |250px | right]] | ||

| + | |||

| + | * [http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/10-gates/00-gates/xor.html Java Applets] demonstrating most logical gates | ||

| + | * [http://www.ti.com/sc/harris Texas Instruments and Harris Semiconductors' Data Sheet Search Engine] | ||

| + | * [http://www.fairchildsemi.com/krkDir/krk.html Fairchild Semiconductors' Data Sheet Search Engine] | ||

| + | * [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls00rev5.pdf 74LS00], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls01rev5.pdf 74LS01], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls02rev5.pdf 74LS02], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls03rev5.pdf 74LS03], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls04rev5.pdf 74LS04], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls05rev5.pdf 74LS05], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls08rev5.pdf 74LS08], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls09rev5.pdf 74LS09], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls10rev5.pdf 74LS10], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls12rev5.pdf 74LS12], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls13rev5.pdf 74LS13], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls15rev5.pdf 74LS15], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls20rev5.pdf 74LS20], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls21rev5.pdf 74LS21], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls22rev5.pdf 74LS22], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls26rev5.pdf 74LS26], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls27rev5.pdf 74LS27], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls28rev5.pdf 74LS28], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls30rev5.pdf 74LS30], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls32rev5.pdf 74LS32], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls33rev5.pdf 74LS33], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls37rev5.pdf 74LS37], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls38rev5.pdf 74LS38], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls40rev5.pdf 74LS40], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls42rev5.pdf 74LS42], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls47rev5.pdf 74LS47], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls48rev5.pdf 74LS48], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls51rev5.pdf 74LS51], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls54rev5.pdf 74LS54], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls55rev5.pdf 74LS55], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls74arev5.pdf 74LS74], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls75rev5.pdf 74LS75], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls76arev5.pdf 74LS76], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls83arev5.pdf 74LS83], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls85rev5.pdf 74LS85], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls86rev5.pdf 74LS86], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls90rev5.pdf 74LS90], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls95brev5.pdf 74LS95], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sn74ls138rev5.pdf 74LS138], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/CD74hct240.pdf 74HCT240], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/sdls145.pdf 74LS243], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/CD74hct244.pdf 74HCT244], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/DM74LS259.pdf 74LS259], [http://cs.smith.edu/~thiebaut/classes/270/datasheets/CD74hct541.pdf 74HCT541] | ||

| + | |||

| + | * [http://cs.smith.edu/~thiebaut/classes/270/datasheets/DM9368.pdf 9368] | ||

| + | * [http://cs.smith.edu/~thiebaut/classes/270/datasheets/nte2114.pdf 2114 1Kx4 RAM] ([[Media:2114_datasheet.pdf | with timing information]] ) | ||

| + | * [[Media:CSC270_75574.pdf | Octal D-Flipflop]] (we do not have these chips in our current collection of chips) | ||

| + | |||

| + | == Motorola 68HC11 Documentation== | ||

| + | [[Image:6811.jpg | right]] | ||

| + | * [http://www.eecs.ucf.edu/undergrad/CpE/labs/EEL4767 Good source of info] on the 6811. | ||

| + | * [http://www.faqs.org/faqs/microcontroller-faq/68hc11/ 6811 FAQs]. | ||

| + | * The official Motorola [http://cs.smith.edu/~thiebaut/classes/270/6811/68hc11a8.pdf | 68HC11A8 Data Sheet]. Fairly cryptic... | ||

| + | * A Motorola [http://www.handyboard.com/techdocs/6811intr.pdf 6811 Manual]. It is a nicely written refresher on many concepts of assembly language applied to the 6811. | ||

| + | ** Check Section 3.2 on addressing modes (inherent, direct, extended, indexed, relative). | ||

| + | ** Get a refresher for the different instruction types (arithmetic, shifts, control, etc) in Section 3.4. | ||

| + | ** The condition code register is covered in Section 3.5. | ||

| + | * [http://cs.smith.edu/~thiebaut/classes/270/6811/68hc11ref-2002.pdf M68HC11 Technical Reference, Motorola] | ||

| + | ** Section 6.5 shows the instructions in logical groups. | ||

| + | * [http://cs.smith.edu/~thiebaut/classes/270/6811/68hc11pocket.pdf M68HC11 Pocket Reference]. | ||

| + | ** Very useful, on Page 15, a list of all the opcodes supported by the 6811, in numerical (hex) order. | ||

| + | * [http://cs.smith.edu/~thiebaut/classes/270/6811/68hc11a8ref.pdf 68HC11A8 Technical Reference]: a hardware and engineering description. of the 6811, its ports, and how it operates. | ||

| + | ** See Section 10 for a cycle-by-cycle description of the execution of each instruction. | ||

| + | ** See Appendix A, Figure A-14 for the timing diagram of a typical (multiplexed expansion) memory access. | ||

| + | |||

| + | <br /> | ||

| + | <br /> | ||

| + | <br /> | ||

---- | ---- | ||

[[CSC270 | Back]] To Main Page | [[CSC270 | Back]] To Main Page | ||

---- | ---- | ||

| + | <br /><br /> | ||

| + | [[Category:CSC270]] | ||

Latest revision as of 08:47, 7 October 2010

Back to Main Page for CSC270

Contents

From xkcd

Prof and TA

|

Dominique Thiébaut email |

The TA for the class is Lei Lei, and her hours and location are available here

Weekly Schedule

Back To Main Page

Links and Resources

Programs

- A Python program that generates a truth table.

Software

PSpice 9

- Pspice 9, Student version. An nice alternative to drawing schematics by hand.

- This is a Windows version. (I have tried to make it work under wine/Mac OS X but haven't been able to make it load the libraries correctly)

- Make sure you select the schematics option when installing the software.

- Select Tools/Schematics when starting the editor

- The schematics editor is located in C:\Program Files\OrCAD_Demo\PSpice\PDesign.exe upon installation.

- Download here!

- PSpice Tutorial

Integrated Circuit Data-Sheets

- Java Applets demonstrating most logical gates

- Texas Instruments and Harris Semiconductors' Data Sheet Search Engine

- Fairchild Semiconductors' Data Sheet Search Engine

- 74LS00, 74LS01, 74LS02, 74LS03, 74LS04, 74LS05, 74LS08, 74LS09, 74LS10, 74LS12, 74LS13, 74LS15, 74LS20, 74LS21, 74LS22, 74LS26, 74LS27, 74LS28, 74LS30, 74LS32, 74LS33, 74LS37, 74LS38, 74LS40, 74LS42, 74LS47, 74LS48, 74LS51, 74LS54, 74LS55, 74LS74, 74LS75, 74LS76, 74LS83, 74LS85, 74LS86, 74LS90, 74LS95, 74LS138, 74HCT240, 74LS243, 74HCT244, 74LS259, 74HCT541

- 9368

- 2114 1Kx4 RAM ( with timing information )

- Octal D-Flipflop (we do not have these chips in our current collection of chips)

Motorola 68HC11 Documentation

- Good source of info on the 6811.

- 6811 FAQs.

- The official Motorola | 68HC11A8 Data Sheet. Fairly cryptic...

- A Motorola 6811 Manual. It is a nicely written refresher on many concepts of assembly language applied to the 6811.

- Check Section 3.2 on addressing modes (inherent, direct, extended, indexed, relative).

- Get a refresher for the different instruction types (arithmetic, shifts, control, etc) in Section 3.4.

- The condition code register is covered in Section 3.5.

- M68HC11 Technical Reference, Motorola

- Section 6.5 shows the instructions in logical groups.

- M68HC11 Pocket Reference.

- Very useful, on Page 15, a list of all the opcodes supported by the 6811, in numerical (hex) order.

- 68HC11A8 Technical Reference: a hardware and engineering description. of the 6811, its ports, and how it operates.

- See Section 10 for a cycle-by-cycle description of the execution of each instruction.

- See Appendix A, Figure A-14 for the timing diagram of a typical (multiplexed expansion) memory access.

Back To Main Page