Line 441:

Line 441: ** [[CSC270 lab 12 2011 | Lab #12]]

** [[CSC270 lab 12 2011 | Lab #12]]

* '''Wednesday'''

* '''Wednesday'''

+ ** Continuation of [[CSC270 lab 12 2011 | Lab #12]]

* '''Friday'''

* '''Friday'''

** [[CSC270 Introduction to the Arduino | Introduction to the Arduino]]

** [[CSC270 Introduction to the Arduino | Introduction to the Arduino]]

Revision as of 10:12, 21 April 2011

--D. Thiebaut 08:44, 7 January 2011 (EST)

Back to Main Page for CSC270

Prof

Dominique Thiébaut email

Weekly Schedule First 1/2 of Semester

Week Topics

Reading

Week 1

Monday : Introduction to the semester

Lecture

Syllabus

Overview of the class

combinational logic (1/4)

sequential logic( 1/4)

microprocessor logic (1/2)

Boolean Algebra

Truth tables

Boolean functions

canonical forms: the minterm canonical form

examples of schematics from Nasa

logic gates

and gate (7408)

or gate (7432)

not gate (7404)

Lab 1

Wednesday : Some basic electricity concepts

Voltages, diagrams, Vcc, Gnd

Measuring voltages: different of potential ==> need two measuring points

Resistors

limit current

passive

property = resistance

unit of resistance = Ohm (Ω)

Ohm's Lay: V = RI

Apply law to simple circuits

Series and Parallel circuits with resistors

Exercises

How to generate a simple switch that generats ON/OFF, High/Low, 1/0

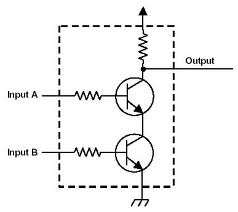

The transistor

Emetter, Base, Collector

basic operations

simple circuit Friday

Example of gates with transistors

Back to boolean functions

Exercise

review of what is a minterm.

Simplifying boolean functions

Maxterms

Binary numbers

Boolean algebra and Logic Gates

Basic theorems

Truth tables

Boolean functions

Canonical forms

Week 2

lecture

What is a switch? i.e. how does a switch from the HeathKit generate a high or low voltage?

We are programmers! Verifying circuits with simple programs !

The binary adder. 2-bit, and 3-bit versions

the NAND and NOR gates: universal gates

lab

Wednesday

Friday : No Class

Week 3

Monday

Wednesday

Lecture

Don't Care conditions in Karnaugh Maps

Decoders

Continuation of Lab #3

Friday : No Class

Karnaugh maps are covered in Chapter 3.

Decoders are covered in Chapter 4.

Week 4

Monday

lecture

another way to draw NANDs and NORs...

relationship between if ( a==b ) { ... }

active-low/active-high signals and circuits

decoders with active-low outputs: most common!

Exercise : Implement f = Σ(1,3,4,5) with a decoder with active-high outputs

Exercise : Implement f = Σ(1,3,4,5) with a decoder with active-low outputs

decoders with an enable input

cascading decoders

designing a 3-to-8 decoder with the 4-to-10 7442 decoder

Lab #4

Wednesday

The Multiplexer circuit

The RS flipflop

Friday

Week 5

lecture

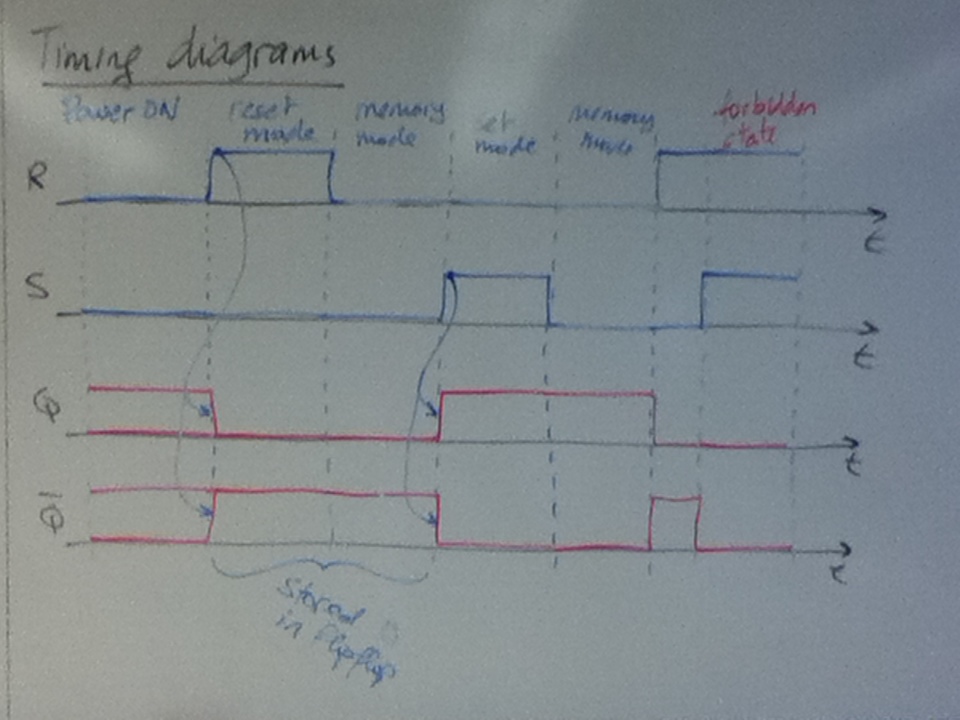

the RS Flipflop

Timing Diagrams

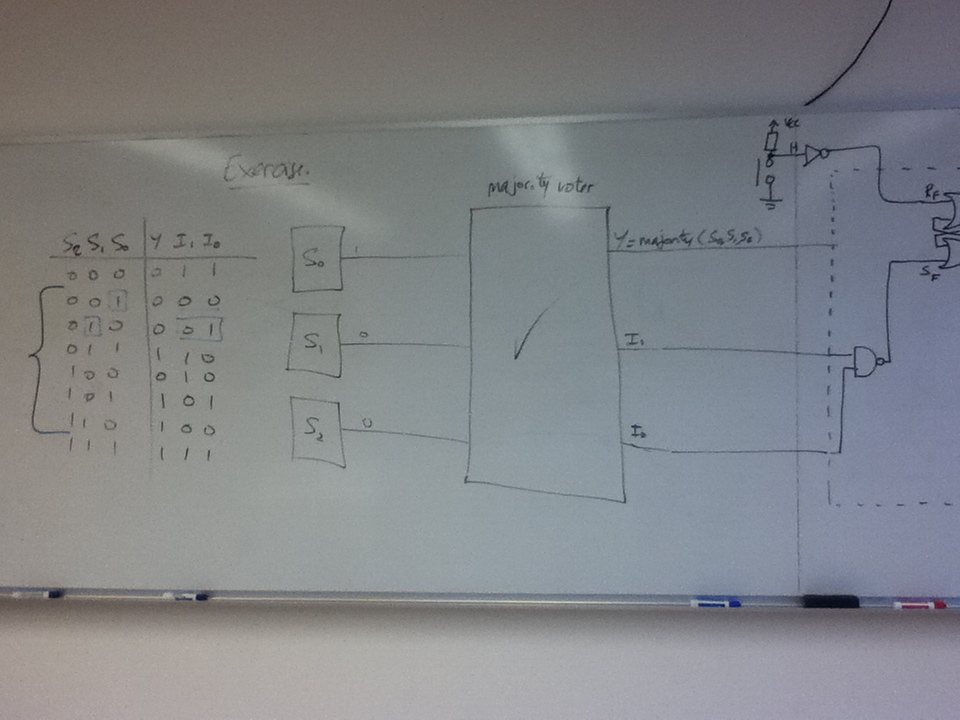

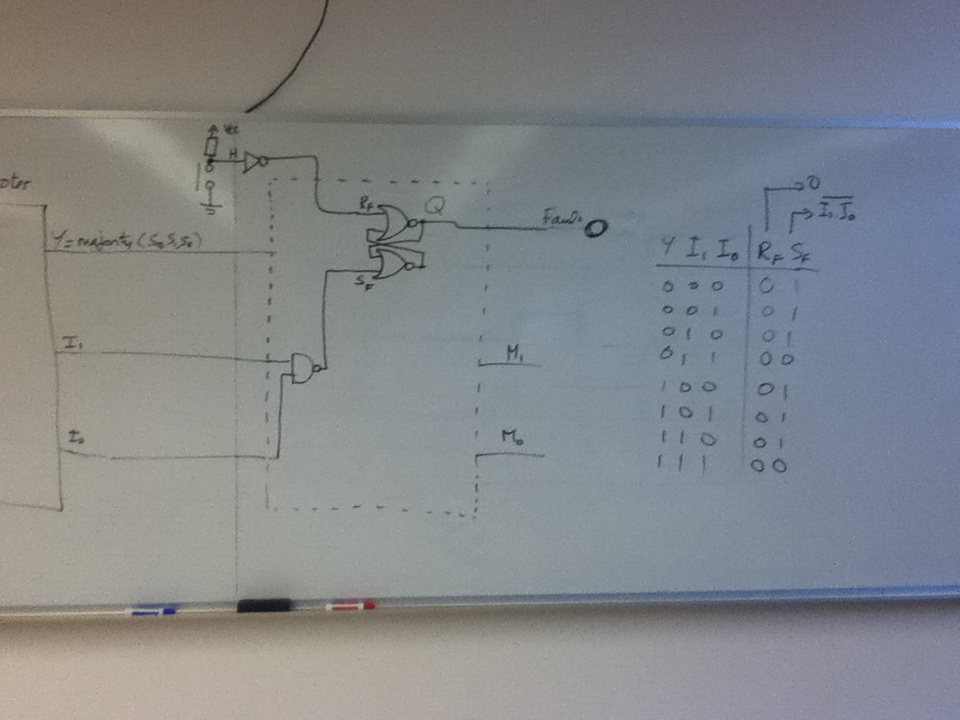

Exercise : Design a majority voter that remembers when a fault occurs. First design a simple one that keeps track of the fact that a fault occurred in the past. Add a reset button to reset the fault signal. Then modify your design so that the majority voter not only remembers that there was a fault, it also remembers the Id of the faulty device. The oscilloscope

Sampling

Periodic signals

Frequence

Peak-to-peak voltages

Trigger: Rule = always trigger on the slower of two signals! Lab #5 Wednesday : Rally Day

Friday The RS Flip-flop: review

Making it work with a clock signal

Ideally we need a pulse to latch information in the flip-flop

Latching on the Low-to-High transition of the clock

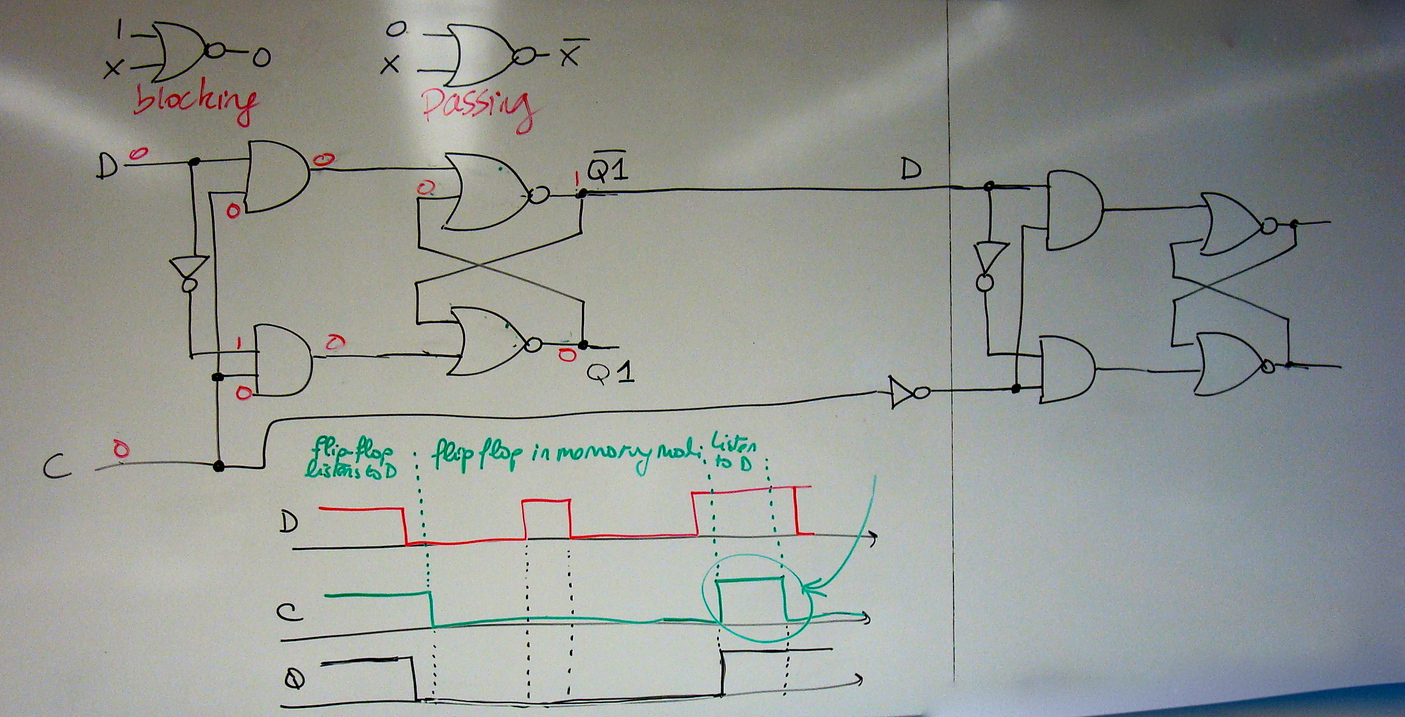

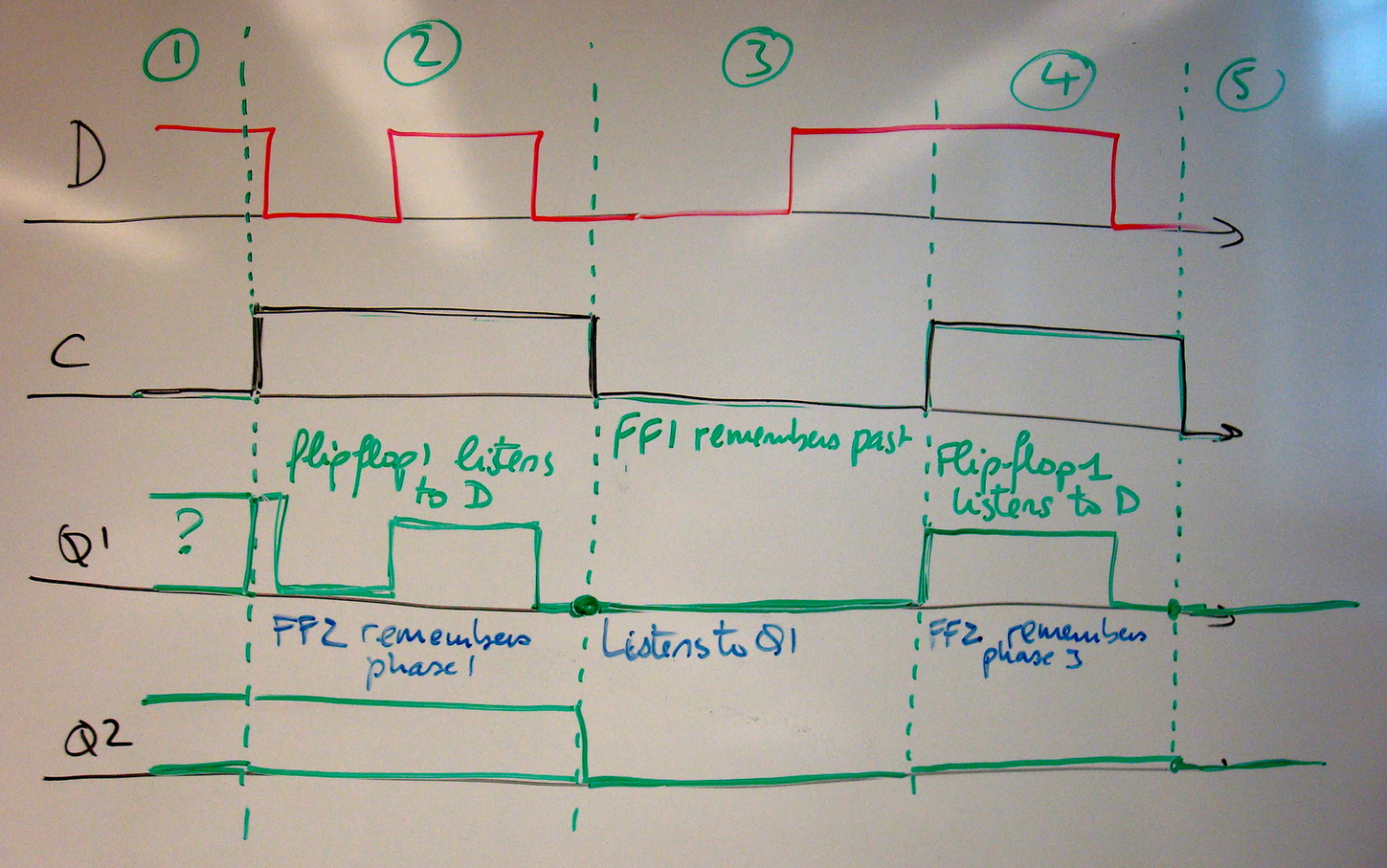

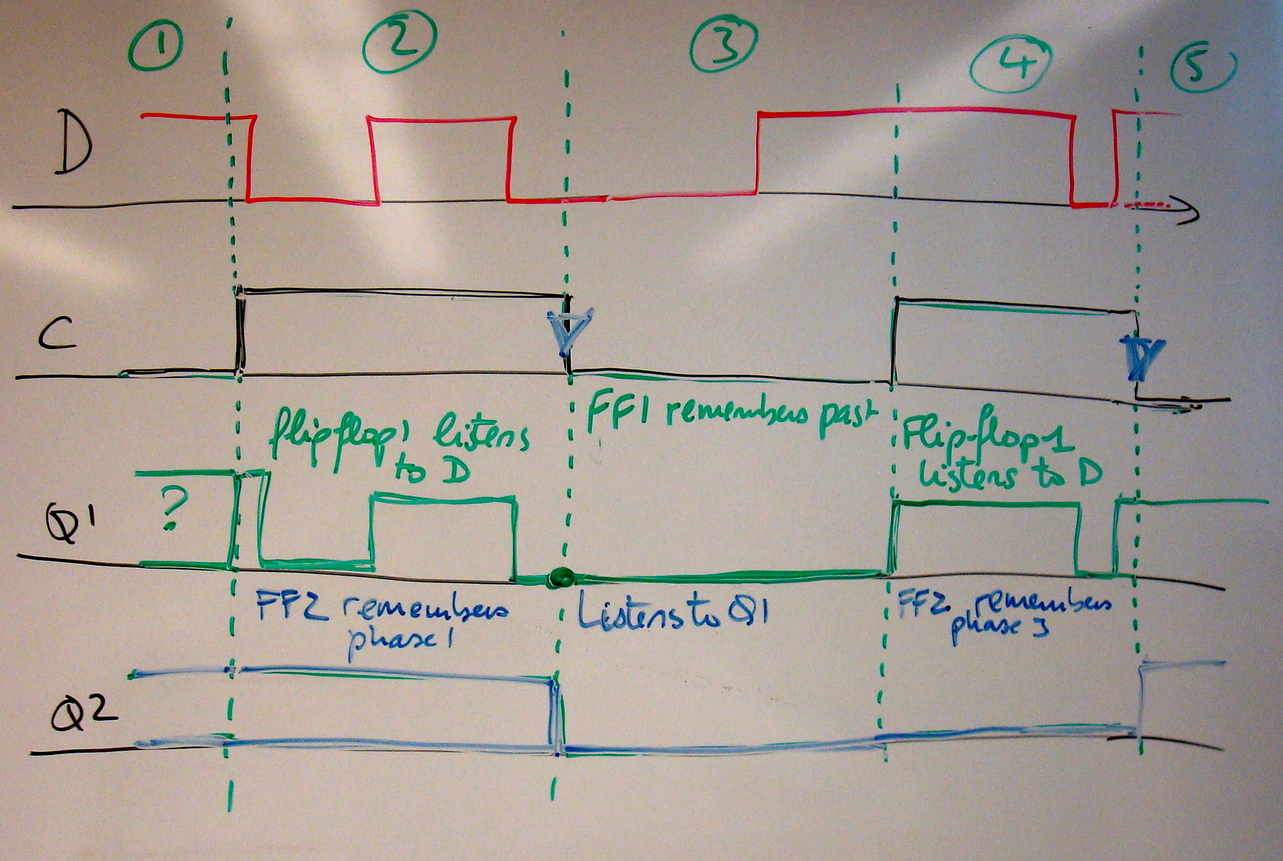

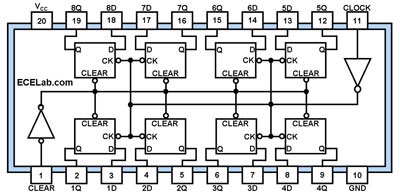

the D Flip-flop: two RS flip-flops working in ping-pong mode

The 74LS74 circuit.

Timing diagram of a D Flip-flop

Mini Lab 1

The D-Flip-flop is covered in Section 5.3 of Mano.

Week 6

Monday

lecture

Low-to-high and High-to-low clock inputs

A first 2-state state-machine with a D-Flip-flop

Duty cycle of a signal = %age of time ON / Period

The Moore Model, or Moore Machine

How do we find a way to generate this machine?

Characteristic Table of the D-Flip-flop

State diagram

State table

Activation table

Lab

Wednesday

Friday

Read Chapter 5

The chapter introduces several flip-flops. We'll look at the JK briefly in class. The chapter also introduces two different approaches to designing finite state machines: the Moore machine and the Mealy machine. We're concentrating here on the Moore machine, for which the output is a function of the present state only. This is the simplest and more widely used model.

Week 7

Monday

Note: The lab report from last Monday (2/28) is due on Wednesday, 3/9/11 to allow extra time to prepare for the midterm.

Midterm Exam

Midterm preparation

Lab #7

2-hour Assembly Crash-Course , Monday 6:00 p.m. - 7:30 p.m., FH 342. RSV if you are coming so that enough pizza can be purchased for dinner.

Wednesday

Sequencers with external inputs

Exercise

Finish Lab #7

Friday

Sequencers with active inputs

Week 8

Second 1/2 of Semester

Week Topics

Reading

Week 9

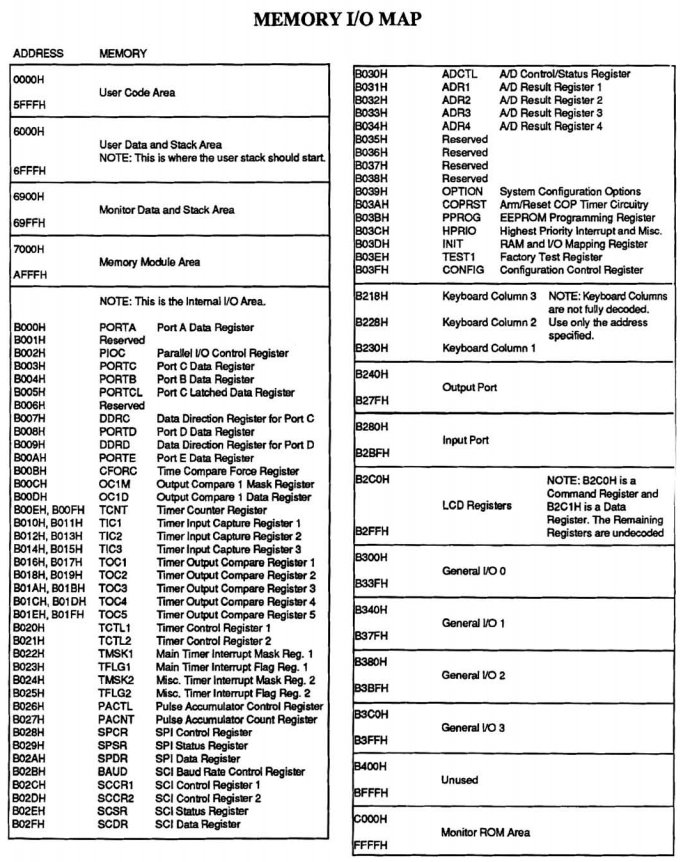

The 6811 Processor: references

The official Motorola 68HC11A8 Data Sheet . Fairly cryptic...

A Motorola 6811 Manual . It is a nicely written refresher on many concepts of assembly language applied to the 6811.

Check Section 3.2 on addressing modes (inherent, direct, extended, indexed, relative).

Get a refresher for the different instruction types (arithmetic, shifts, control, etc) in Section 3.4.

The condition code register is covered in Section 3.5. Skip Section 4.

M68HC11 Technical Reference , from Motorola.

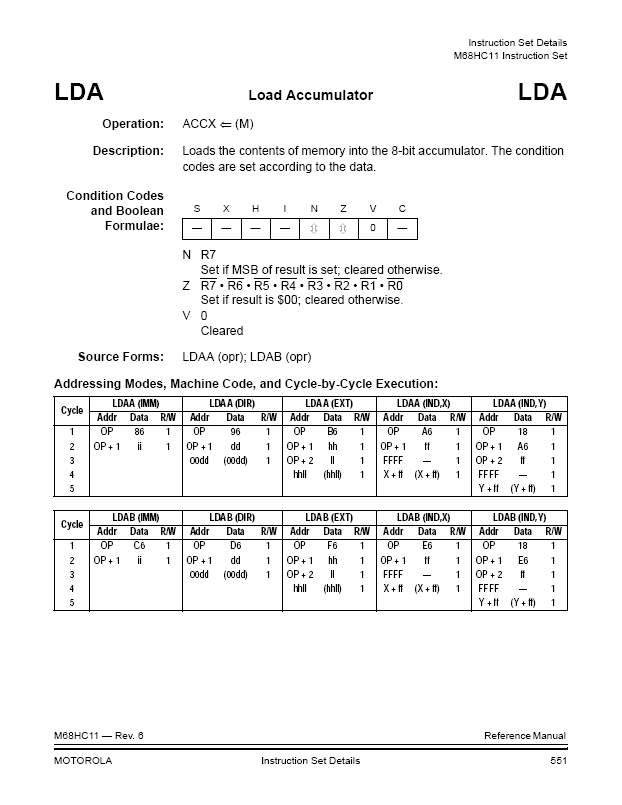

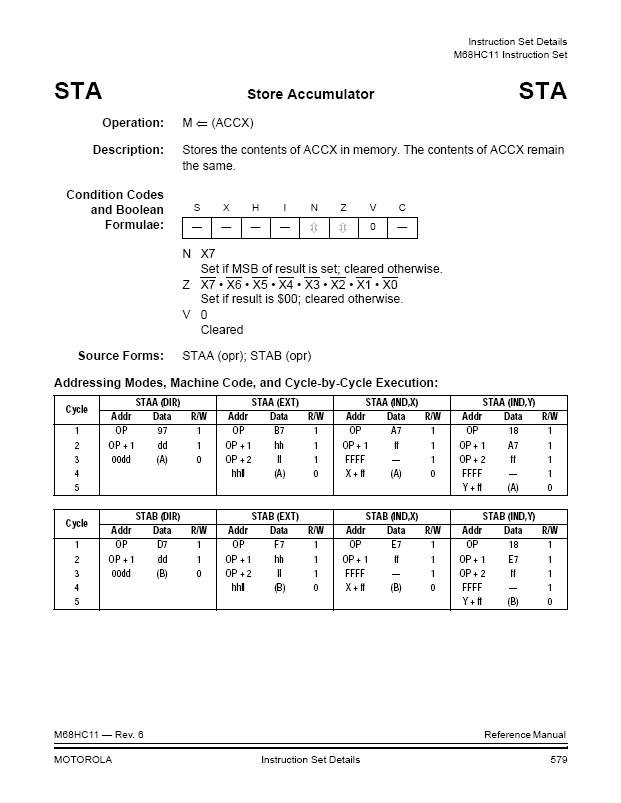

Section 6.5 shows the instructions in logical groups.

M68HC11 Pocket Reference .

Very useful, on Page 15, a list of all the opcodes supported by the 6811, in numerical (hex) order.

68HC11A8 Technical Reference : a hardware & engineering description. of the 6811, its ports, and how it operates.

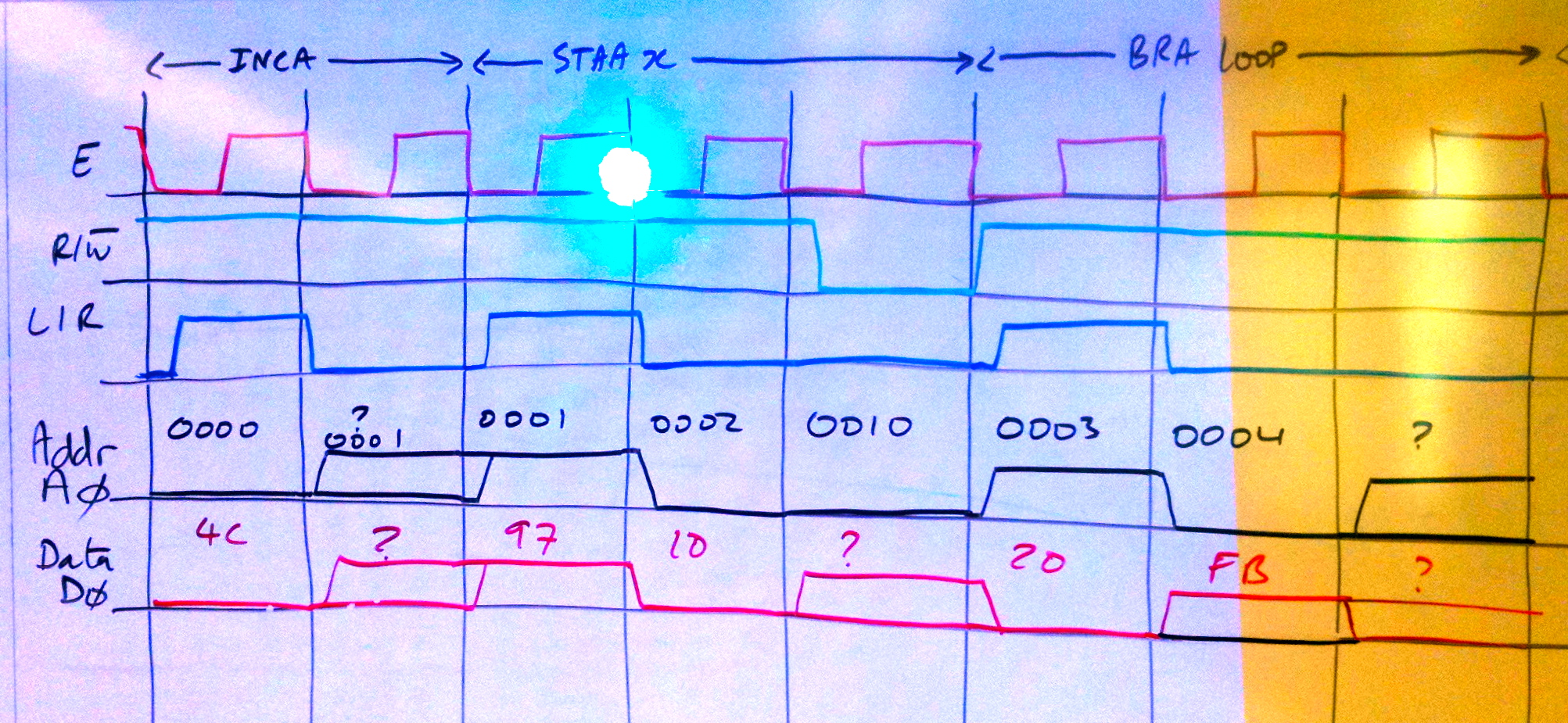

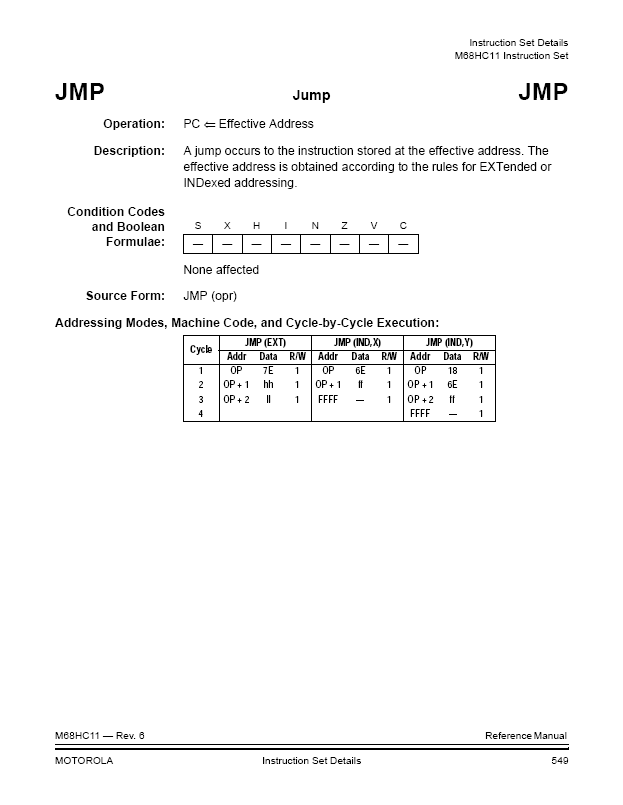

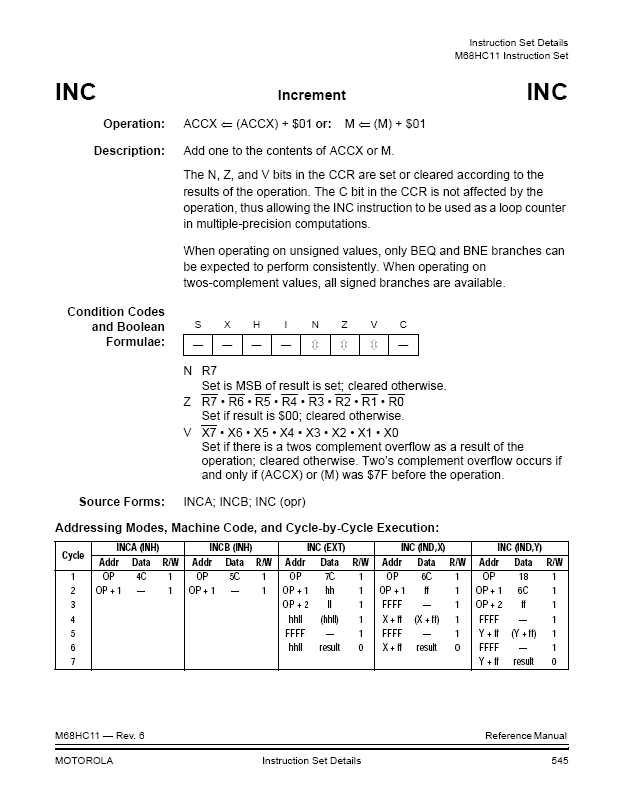

See Section 10 for a cycle-by-cycle description of the execution of each instruction.

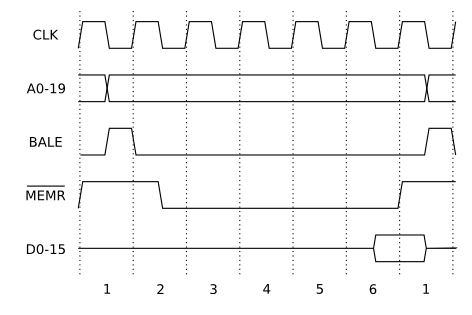

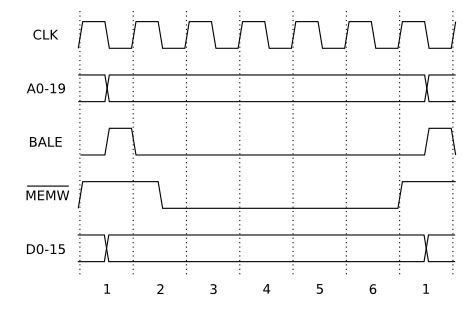

See Appendix A, Figure A-14 for the timing diagram of a typical (multiplexed expansion) memory access.

6811 Instruction Set , with hexadecimal opcodes. A reverse map, from hex to instructions can be found here.

2-Page List of all the 6811 Instructions

Software for the 6811

Heathkit ETW3800 Trainer manual (pdf) Concentration on Assembly Language

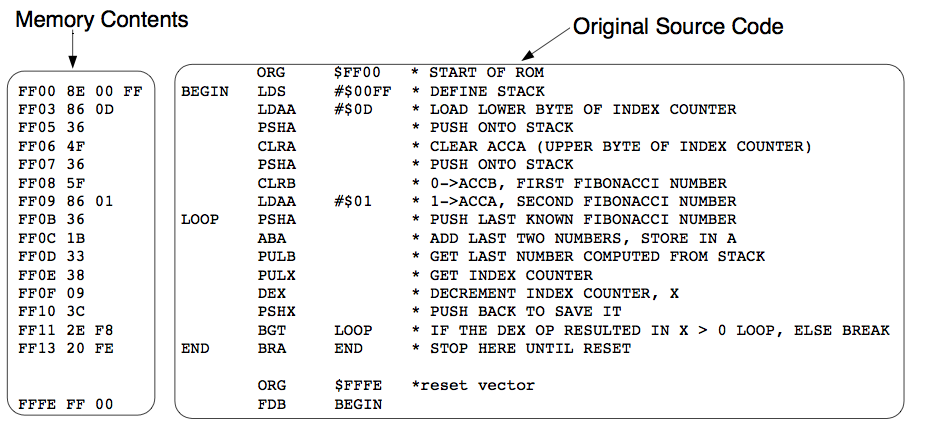

Example of fully assembled 6800 program

Listing format

opcodes, mnemonics, directives, columnar format

The instructions

Addressing Modes: inherent, immediate, direct, extended, indexed, relative Wednesday

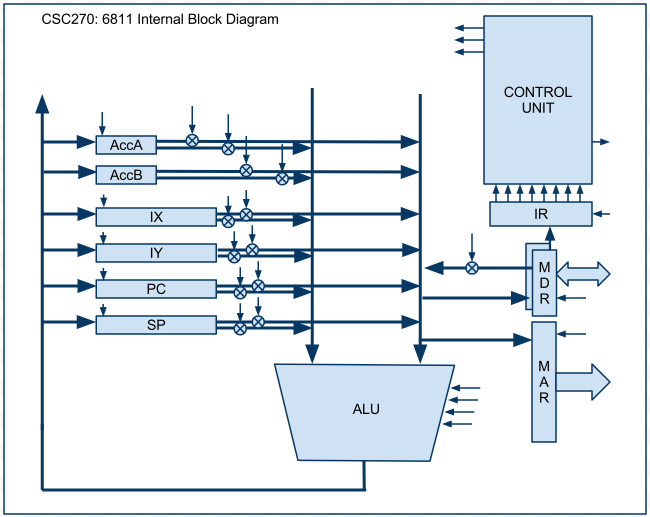

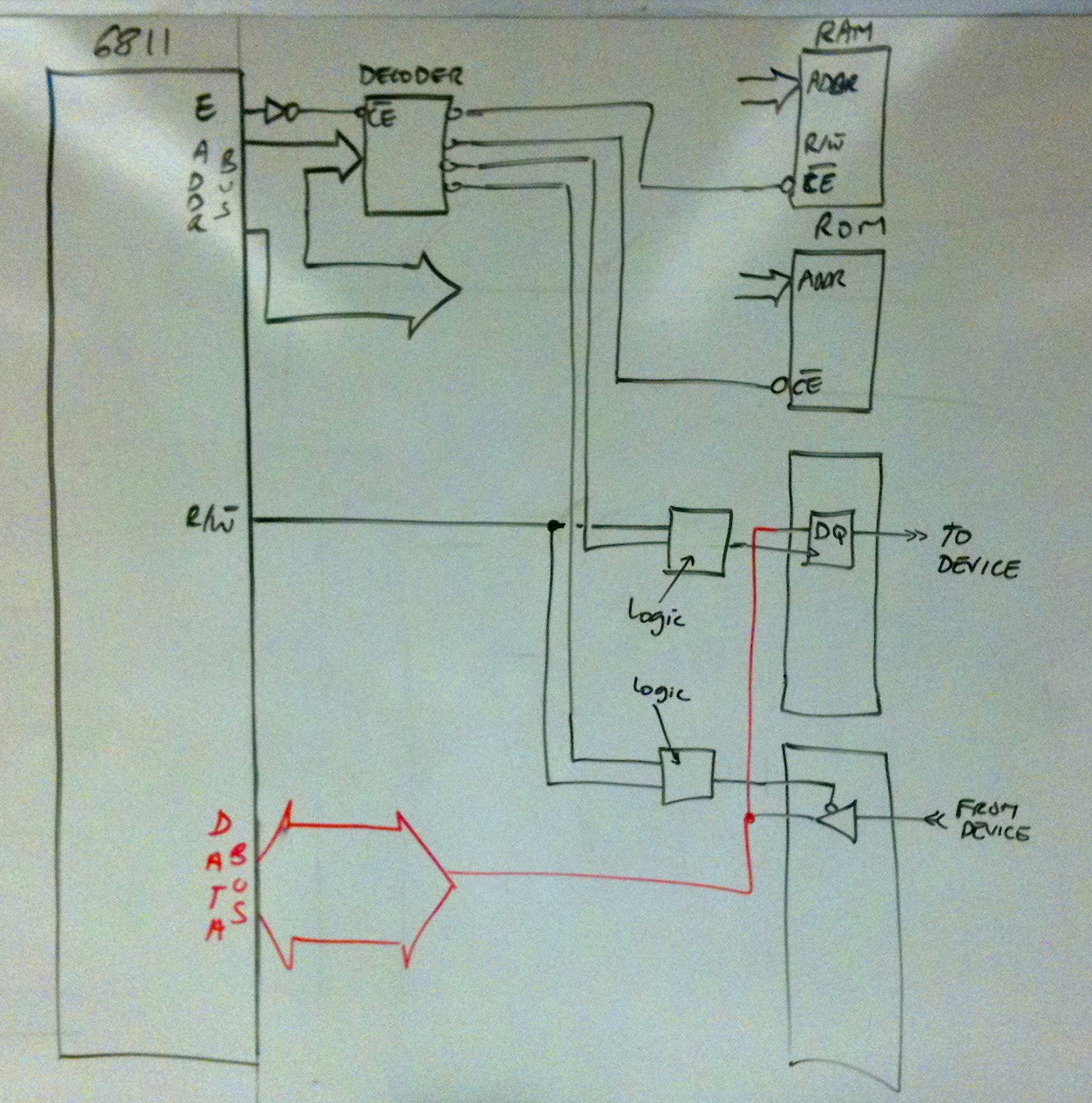

A look at the internal circuits of the 6811.

Week 10

Monday

lecture

Quiz

Cycle-by-cycle description of an endless loop of 3 instructions: 0000 4C LOOP: INCA

0001 97 10 STAA x

0003 20 FB BRA LOOP

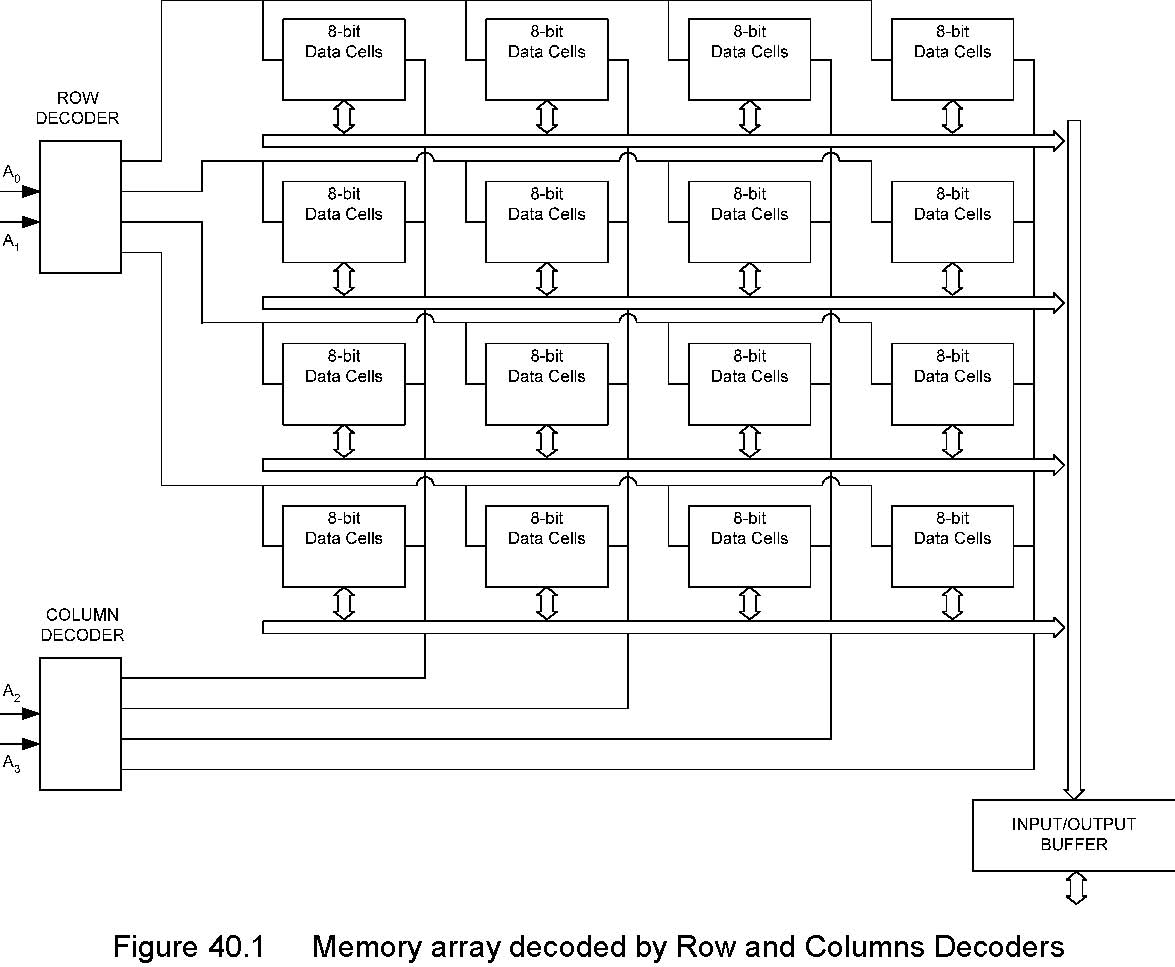

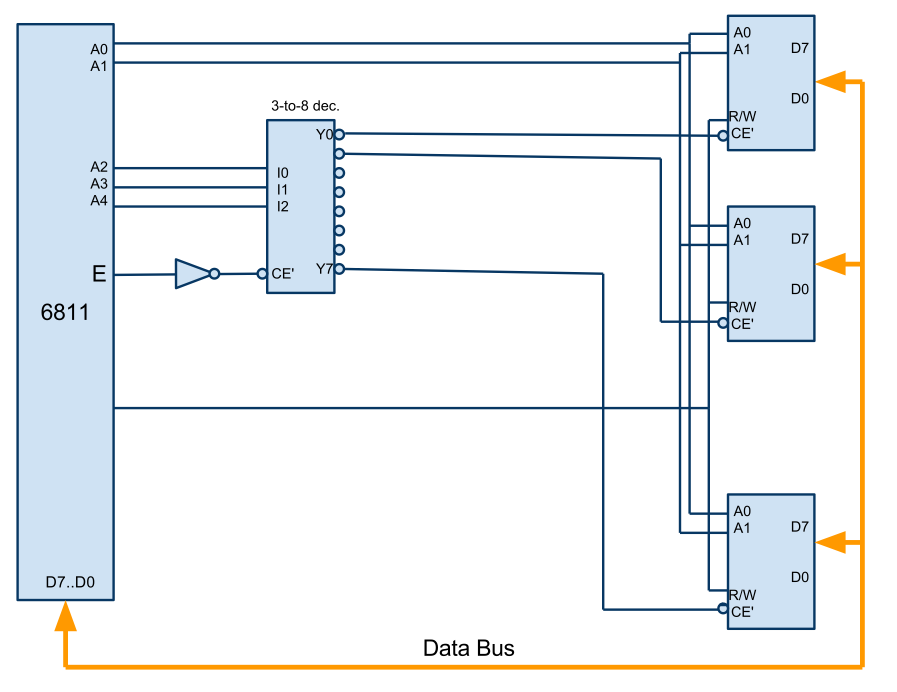

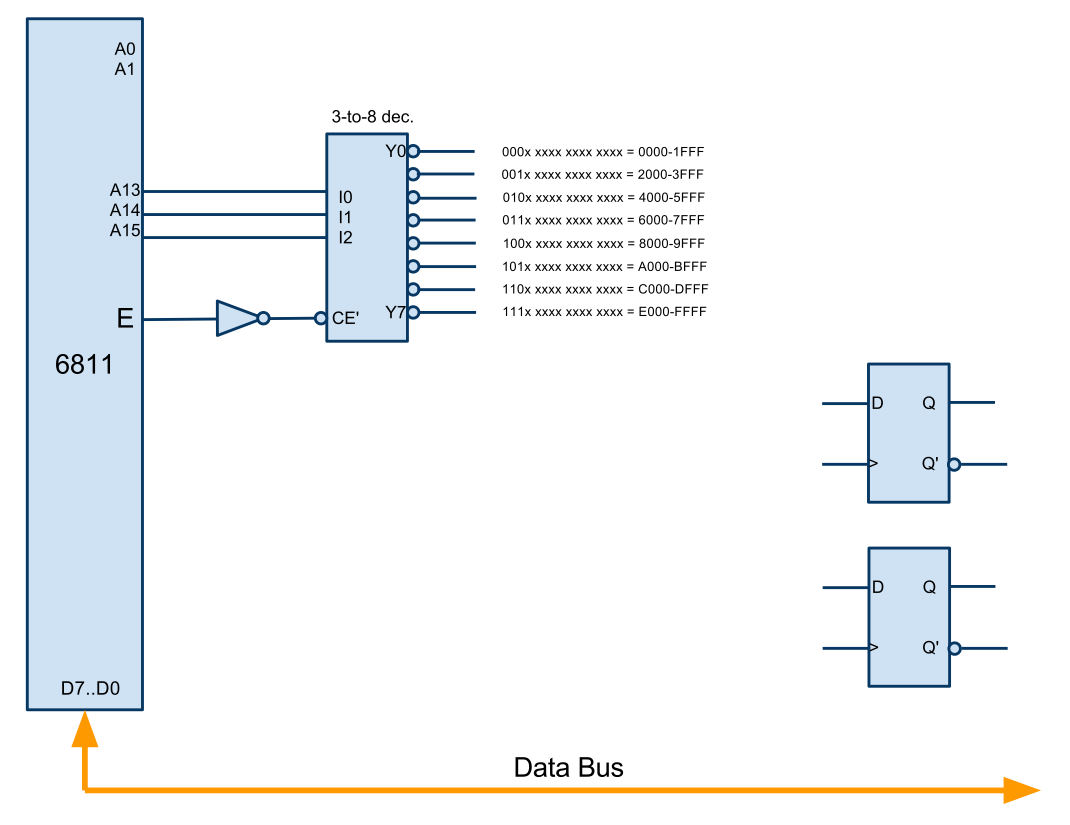

Wednesday : MEMORY-MAPPED I/O

Friday

Happy Birthday Edo! (all the pics on Facebook )

Week 11

Monday

Wednesday

Designing a 2-bit I/O port : 2 solutions

Parallel-write design (the 2 bits have the same address)

Separate-address design (the 2 bits have different addresses)

Continue with Lab 10

Friday

Week 12

Happy Birthday Millie! (all pictures on Facebook .)

Monday

lecture

Lab 11

Designing and wiring up an input port with the 6811 How to figure out how many different addresses energize Y4?

Examples of I/O Ports

Parallel Port

Data Registers

Control Registers

Status Registers

Handshake Protocol

Software Driver Friday : No class: Programming Contest!

Week 13

Monday (in FH345: lab shared with Susan Voss's class)

Wednesday

Friday

Week 14

Please watch on your own the very good Arduino video.

Back To Main Page

Links and Resources Printing How to print a text file (pure ASCII, not an MS Word document) from a beowulf account to the printer @ FH354: cprint -15 myFile.txt

How to print a pdf from a beowulf account to the printer @ FH354: lpr -P ford354 max232.pdf

How to print an image to the same printer, from a beowulf account: convert myImage.jpg myImage.pdf

lpr -P ford354 myImage.pdf

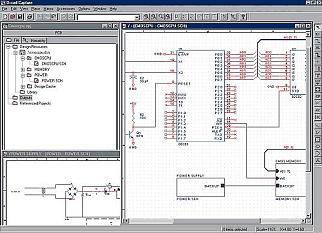

Programs Software PSpice 9 Pspice 9, Student version. An nice alternative to drawing schematics by hand.

This is a Windows version. (I have tried to make it work under wine/Mac OS X but haven't been able to make it load the libraries correctly)

Make sure you select the schematics option when installing the software.

Select Tools/Schematics when starting the editor

The schematics editor is located in C:\Program Files\OrCAD_Demo\PSpice\PDesign.exe upon installation.

Download here !

PSpice Tutorial Integrated Circuit Data-Sheets Java Applets demonstrating most logical gates

Texas Instruments and Harris Semiconductors' Data Sheet Search Engine

Fairchild Semiconductors' Data Sheet Search Engine

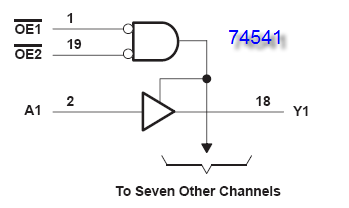

74LS00 , 74LS01 , 74LS02 , 74LS03 , 74LS04 , 74LS05 , 74LS08 , 74LS09 , 74LS10 , 74LS12 , 74LS13 , 74LS15 , 74LS20 , 74LS21 , 74LS22 , 74LS26 , 74LS27 , 74LS28 , 74LS30 , 74LS32 , 74LS33 , 74LS37 , 74LS38 , 74LS40 , 74LS42 , 74LS47 , 74LS48 , 74LS51 , 74LS54 , 74LS55 , 74LS74 , 74LS75 , 74LS76 , 74LS83 , 74LS85 , 74LS86 , 74LS90 , 74LS95 , 74LS138 , 74HCT240 , 74LS243 , 74HCT244 , 74LS259 , 74HCT541 Motorola 68HC11 Documentation Good source of info on the 6811.

6811 FAQs .

The official Motorola | 68HC11A8 Data Sheet . Fairly cryptic...

A Motorola 6811 Manual . It is a nicely written refresher on many concepts of assembly language applied to the 6811.

Check Section 3.2 on addressing modes (inherent, direct, extended, indexed, relative).

Get a refresher for the different instruction types (arithmetic, shifts, control, etc) in Section 3.4.

The condition code register is covered in Section 3.5.

M68HC11 Technical Reference, Motorola

Section 6.5 shows the instructions in logical groups.

M68HC11 Pocket Reference .

Very useful, on Page 15, a list of all the opcodes supported by the 6811, in numerical (hex) order.

68HC11A8 Technical Reference : a hardware and engineering description. of the 6811, its ports, and how it operates.

See Section 10 for a cycle-by-cycle description of the execution of each instruction.

See Appendix A, Figure A-14 for the timing diagram of a typical (multiplexed expansion) memory access.

Heathkit ETW3800 Trainer manual (pdf)

Input/Output with the 6811: Memory-Mapped I/O (Heathkit documentation)

Back To Main Page